|

|

|

CLOCKS SI REGISTRE

Scop:

cod VHDL pentru a detecta fronturi pentru clock ;

proiectarea si sinteza circuitelor logice secventiale ;

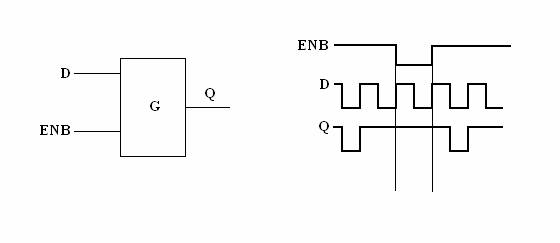

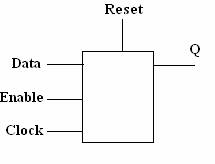

LATCH TRANSPARENT

Vezi ex 1.

Din analiza proceselor combinationale rezulta ca atunci cand o iesire a procesului este asignata doar pentru un subset al intrarilor,atunci :

Semnalul de intrare care poate schimba iesirea Q este ENB='1';

Daca ENB='0',asignarea nu se executa ;

Cand ENB='1',orice schimbare in D este reflectata in Q;ENB si Q se gasesc in lista de senzitivitate(sensitivity list) ;

acesta este cazul unei asignari incomplete.

La sinteza rezulta un latch.

Nota : 2 reguli pentru sinteza latch :

lista de senzitivitate trebuie sa fie completa(sa contina toate intrarile) ;

nu exista reactii in cazul proceselor(nici un semnal sau variabila nu e citita inainte de a fi asignata) ;

Nota :in sinteza cu FPGA nu

se recomanda.In sinteza cu ASIC se poate.Acestea se intampla deoarece

implementarea are o reactie asincrona.

Recomandare :sa se verifice data

sheat pentru componenta suport aleasa pentru implementare inainte de a incepe

sa se scrie in VHDL.

Problema :cum modific cod VHDL pentru ca asignarea Q sa aiba loc :

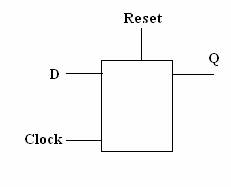

BISTABILE CU DECLANSARE PE FRONT

Cod VHDL pentru bistabile declansate pe front :o solutie simpla este inlaturarea lui D din sensitivity list .Este corect pentru simulare,dar nerecomandat pentru sinteza deoarece la sinteza, cele mai multe pachete ignora sensitivity list.In concluzie,bistabilele nu se pot sintetiza.In acest caz,raspunsul pentru sinteza bistabilelor declansate pe front este utilizarea atributului pentru semnale :EVENT.

EVENT este de tip boolean(TRUE,FALSE).

EVENT='TRUE'pe durata unui delta delay cand intrarea respectiva comuta.

Conditia :clock'Event and Clock='1' =TRUE cand s-a schimbat clock-ul.

Rising

Edge

Rising

Edge

Cncluzie:la sinteza ,orice semnal asignat pe frontul clock va fi sintetizat ca un bistabil :

Falling Edge

Falling Edge

clock'Event clock='0'.

Ex. : process(A)

Begin if B'Event and C'Event then

Q<=D;

End if;

End process

In ce conditii Q poate sa fie asignat cu D?

FRONTURI RIDICATOARE

Ex.:package STD_LOGIC_1164.all include functiile standard

Rising_edge: ![]()

Falling_edge: ![]()

Diferenta:

If clock'Event and clock='1' then : ![]() H,( O,L,X);

H,( O,L,X);

If Rising_edge (clock) then:  1 or H,(doar O sau L);

1 or H,(doar O sau L);

If clock'Event and clock='1' then este valid la o tranzitie a clock-ului.

La sinteza,in cele mai multe cazuri:apar bistabile.

![]()

RESET ASINCRON

Reset signal sensitivity list ;

Test nivel reset inainte de test clock front.

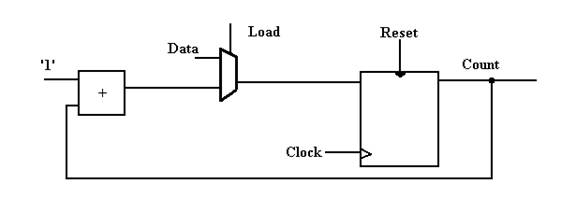

Ex.4:Structura este clasica pentru implementari de functiuni secventiale :in lista de senzitivitate apare clock-ul si semnalele asincrone(resetul).Prima testata cu if este intrarea asincrona.Dupa else if risinf edge(clock),toate functiile sunt sincrone cu frontul ridicator al clock-ului.Aici pot folosi clock-uri pentru a forta prioritati if de executie.Case este un table sin u forteaza prioritati.

Asignarea vectorului count este data de mux.Load :semnal prioritar fata de count+1 pentru ca este primul testat in if.

In FPGA exista un reset global dedicat care trebuie asignat explicit.Dezavantaj:reduce portabilitatea,resetul global depinzand de tehnologia de implementare utilizata la sinteza.Procesul din ex.5 reprezinta un bistabil sau registru D functie de DATA si Q.

5 VALIDARE CLOCK

Exista tehnologii (in special FPGA) care dispun de o intrare dedicata pentru validare clock.

Ex.6 :resetul este sincron cu tactul si este prioritar fata de functia de bistabil D(enable=validare clock) ;

Ex.7 :enable este prioritar ;

Nota :in sensitivity list exista clock + in asincrone.

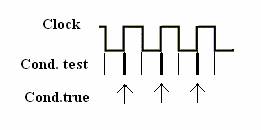

6 WAIT UNTIL

wait for σ :suspenda procesul pentru σ time (interval de timp fixat).

Wait until conditie : suspenda procesul pana cand cond=TRUE.Conditie=expresie booleana.

Ex.8:Daca nu apare nimic in lista de senzitivitate, clock-ul este implicit.

Conditia este testata doar la aparitia unui eveniment in semnalul conditie.

Lista de senzitivitate pentru wait are un singur semnal clock- implicit.Procesul este suspendat pana cand apare un eveniment (frontul ridicator al tactului),se executa ce este dupa wait until,se cicleaza procesul la inceput se ajunge din nou la wait until dupa care procesul se suspenda.Instructiile sunt evenimente triggerate,nu sunt sensibile la nivel.

Loop la inceput ;ex.:wait suspenda procesul .

Ex.9 este echivalent cu 8 doar ca se utilizeaza clock-ul care este implicit,se foloseste pentru sincronizare wait until RISINGEDGE (test pe front,pleaca de la nivel la nivel).

TEMPLATES (MODELE) PENTRU SINTEZA,SECVENTIALE

Scop:prezinta 5 tipuri de modele recomandate pentru utilizarea procese.Se pot folosi si alte stiluri,dar nu dau rezultate bune pentru toate pachetele VHDL.

Ex.10

T1 :logica combinationala pura :multiplexoare,decodificatoare,respecta cele 3 reguli :

1.lista de senzitivitate trebuie sa fie completa.

2.nu trebuie sa existe asignare incompleta pentru if si case .

3.nu trebuie sa existe reactii.

T2 :se refera la implementare de latch transparente :

Procesul continue doar un if care trebuie sa testeze nivelul lui enable.

In corpul lui if se respecta regulile 1 si 3.

Ex.12

T3,T4 :utilizate pentru bistabile :trebuie realizata sincronizarea cu frontul clock-ului in doua stiluri :if risingedge sau wait until(se recomanda if risingedge).Nu exista else in acest if,nu sunt alte linii dupa endif.

Ex.13:este echivalent cu 12;este de ales T3 pentru ca se recomanda if risingedge.

Ex.14

T5 :control asincron al intrarilor:intrarile asincrone trebuie sa apara in lista de senzitivitate alaturi de clock.Intrarea asincrona este testata prima in if,ea este prioritara.Pentru sincronizare se utilizeaza risingedge.Toate instructiile dupa rising sunt sincronizate cu frontul ridicator.Nu exista else la if ci doar elseif.Nu sunt instructii dupa endif.Urmeaza end process ca la T4.

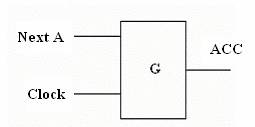

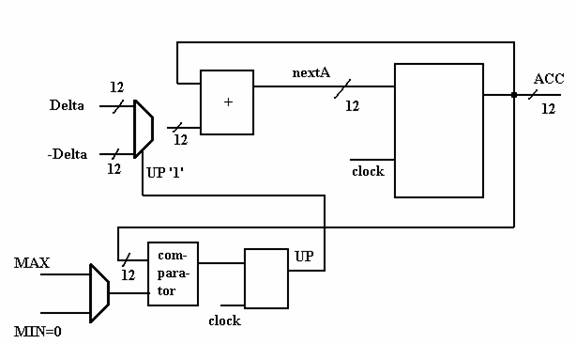

IMPLEMENTARI DE REGISTRE (RTL : register transfer level)

Ex.15 ce bistabile sunt sintetizate?

Orice signal asignat in proces si sincronizat cu clock-ul va fi sintetizat ca bistabil pe front pentru ca valoarea sa se poate schimba numai pe frontul clock.

ACC reprezinta semnal asignat pe penultima linie(numarul de BS ACC type =2)

Variabilele asignate in proces sunt candidate sa fie sintetizate ca BS.

Variabilele pot fi sintetizate fie ca un registru,fie ca un fir.

NextA este sintetizat ca fir(bus).Variabilele care sunt asignate cu o noua valoare inainte de a fi citite in cadrul procesului sunt asignate ca fire.

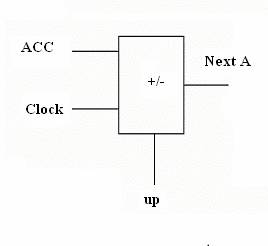

Up :se utilizeaza ca bistabil pentru ca este citit inainte de a fi asignat.O modalitate pentru modificarea pantei de numarare este :

Modific incrementul numaratorului ;

Modific frecventa clock-ului.

Concluzie :

Intrebari : ce functie indeplineste Ex.15 ?care este evolutia in timp a lui ACC pentru intrari constante cu clock cu perioada constanta ?

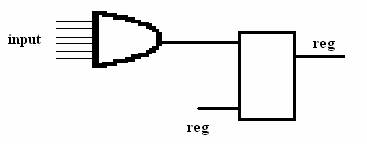

Cate registre se sintetizeaza din procesul de la ex.16 ?

Candidati :signal reg. , v =>un bistabil

Ex.16 :

Reg : Signal asignat in proces dupa sincronizare,inseamna ca este bistabil.

V :variable,asignat inainte de a fi citit,inseamna ca este fir.

Ce functie indeplineste Ex.16 ?

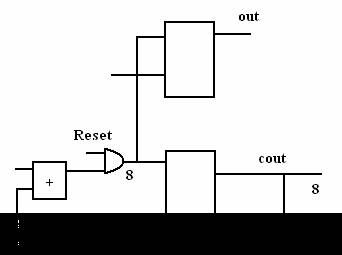

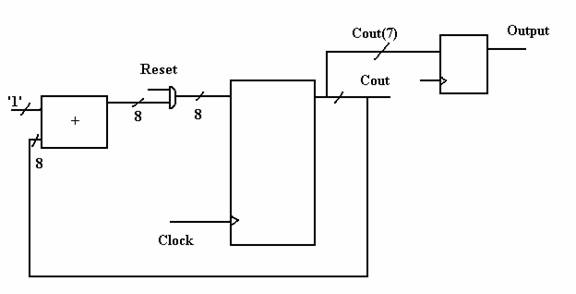

Ex.17

Cate bistabile sunt sintetizate la Ex.17 ?

La nivelul primei etape din cadrul unui proiect VHDL trebuie declarat IEEE.NUMERIC.STD.all.Pentru out se sintetizeaza un bistabil de 1 bit.Inseamna ca in total se sintetizeaza 9 bistabile(8 pentru count).

EVITAREA BISTABILELOR NEDORITE

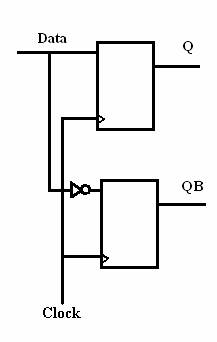

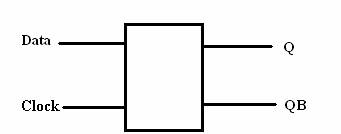

Ex.18 :cum scriu codul pentru sinteza unui bistabil.

Ex.19 :genereaza evitarea bistabilelor nedorite astfel :QB este in afara procesului.Avem in singur bistabil.QB este sintetizat ca logica combinationala.

Ex.20 :if UPOUT='1' :ilegal.Exemplul este gresit.

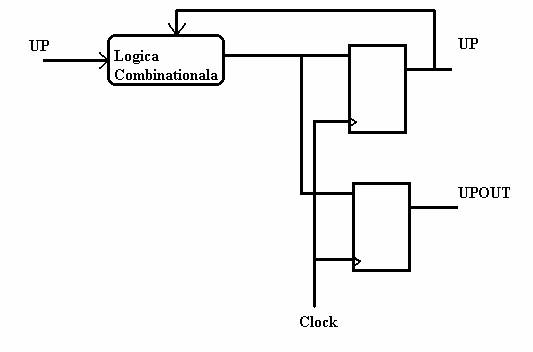

Ex.21 :introduce o variabila suplimentara UP in cadrul procesului care va inlatura greseala de la Ex.20.Aici avem 2 bistabile.Dezavantaj :variabila UP se sincronizeaza printr-un bistabil in plus.

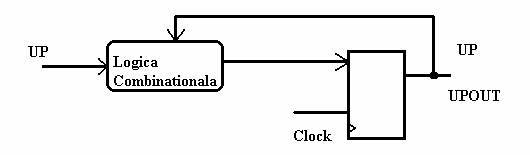

Ex.22 :dezvolta ideea de la 19.UPOUT il aloca in afara procesului.

Ex.23 :UPOUT este declarat de tip buffer.Comparativ cu Ex.20 este corect,buffer-ul putand fi citit si asignat.