|

|

|

STARI SECVENTIALE

Starile secventiale sunt scrise in cadrul proceselor,fiind utilizate intens pentru a descrie hardware-ul pentru sinteza si vectorii de test.

1 Variabile

Sunt valori care au fost memorate in signals,semnale ce fac parte din cadrul unei arhitecturi.

Memorarea la nivel de proces se face in variabile.

Signals :reprezinta in mod normal conexiuni electrice(tronsoane de fire).

Variabile :pot avea aceasta functie,dar pot fi mai abstracte :pot reprezenta fire,registre sau pot memora valori intermediare in calcule abstracte.

Variabila este un obiect ce permite memorarea de valori in cadrul procesului.O variabila este declarata in cadrul procesului si poate fi utilizata doar in acel proces(variabila locala)

Sintaxa :

Variable Nume_variabila ,. :data_type[] ;

(asignarea)

Variabila se poate schimba prin alocarea variabilei ( :=).

Asignarea variabilelor se petrece secvential (begin end) si schimba valoarea variabilei imediat.

Remarca:comportarea variabilei este diferita comparativ cu signal,astfel :

Asignarea variabilelor nu are niciodata delay.

Asignarea semnalelor au tot timpul delay(chiar daca este delta delay).

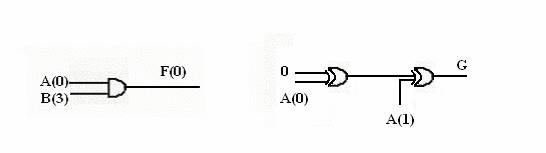

La sinteza procesului orice asignare de variabila creeaza un nou nivel logic :

Variabila definita inauntrul procesului poate fi definita numai local (in proces) ;

Pentru a transmite valoarea intre procese,trebiue utilizat signal,nu variable.

4.2 IF

Sintaxa:

If condition_logic then

Stari secventiale;

[elsif condition then

stari secventiale.;]

[else

stari secventiale;]

end_if;

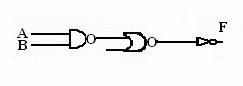

Pentru exemplul 3:

Pentru exemplul 4:

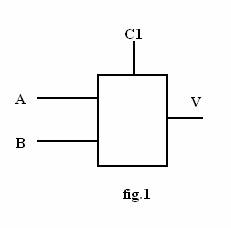

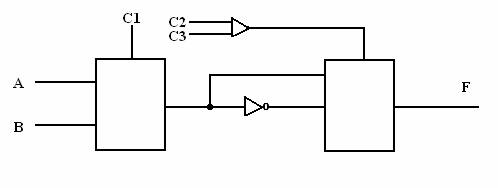

1. Sinteza if : multiplexeaza orice signal sau variabila asignata in cadrul if.

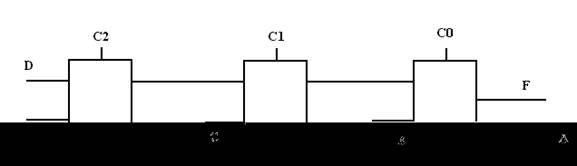

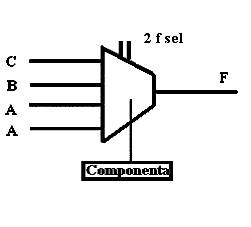

Conditia selecteaza intrarea pentru multiplexor (fig.1).

Toate intrarile din figura de mai sus apar in sensitivity list a procesului.

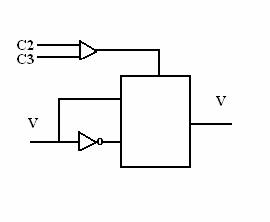

2. If incuibate(nested) : pornesc de la coada spre inceput:

3. Alternativa de scriere condensata: elsif : permite teste multiple cascadate : se executa numai ramura conditiei logice adevarate.(2=3/condensat).

4.

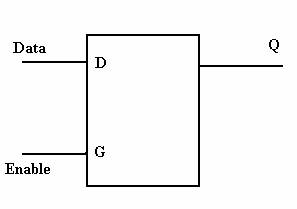

Aici are loc o asignare incompleta (caz practic).Poarta numele de latch transparent.Pentru enable=0,Q=vechiul Q.

Nota la regula 3: nu se utilizeaza if-uri incomplete

4.3 Case

Reprezinta o stare secventiala,alternativa pentru if.

Sintaxa:

Case Expr_logica is

when choice|choice|choice.=>stari secventiale;

when choice|choice|choice.=>stari secventiale;

.

end_case;

Expresia este evaluata si comparata cu expresia din dreptul lui choice.Cand expresia coincide cu choice, se executa corpul ( stari secventiale) si apoi se sare la end_case.

Others: 'x v z' '(.)'

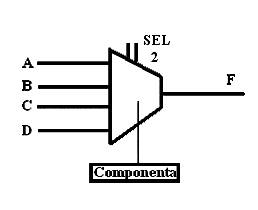

Orice caz posibil al expresiei acoperite prin when apare o singura data la sinteza ceea ce reprezinta un caz foarte similar cu if.

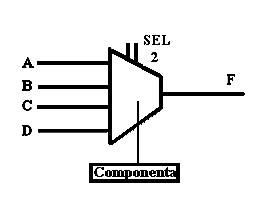

Orice signal sau variabila asignata este multiplexata.

4 Comparatia si utilizarea if-case

If este testata secvential : pot aloca intrari intrari prioritare.

Case este testata in paralel,ceea ce duce la o simulare mai rapida.

Pentru FPGA ,sinteza cu elsif nu este recomandata deoarece multe nivele reprezinta o implementare neoptima.

Recomandare :case pentru decodarea unor intrari.

4.5 For loop

Sintaxa:

[eticheta:] for loop param. In Range loop

stari secventiale;

end_loop [eticheta];

For loop : executa un set de instructii secventiale controlate de loop_parametru.0 to 3 ;3 to 0:range ascendent or descendent(range=rang). Rangul este crescator pentru 0 to 3(de la 0 la 3) si descrescator pentru 3 to 0(de la 3 la 0).Incrementul este fix si are valoarea +1 sau -1. Vezi ex. 16.

Nota : I (incrementul) nu se poate schimba in corpul for prin asignare fortata ceea ce

inseamna ca nu pot iesi fortat din bucla for.

I se utilizeaza local si nu in afara lui loop.

Vezi ex 17.

Variabila I nu este vizibila in cadrul for pentru ca este blocata de loop parametru I cu acel nume .

In for,I=0,1,,3.Variabila I se initializeaza cu prima valoare din lista STD_LOGIC,adica 0;inainte de end_process,I va deveni 1.Vezi ex 18.

Starile secventiale din for sunt sintetizate prin copii multiplicate.Pentru fiecare valoare a parametrului rezulta o copie.

Remarca :Range fixat=const.pentru sinteza.

4.6 Loops( bucle)

Exista trei tipuri:

1 : for parametru in loop_range is

stari secv.;

end_loop;

2 : while conditie loop

stari secv.;

end_loop;

3 : loop

bucla infinita;

end_loop;

while: se iese din bucla cand conditie=0.

Remarca:doar for loop este sintetizabila,daca range =fixat.Celelalte loop se afla in test benches sau la modele inaintea RTL.

Loop-exit;exit when conditie valabila pentru toate cele 3 loop.

For loop :eticheta pentru a indica care bucla se paraseste.

Salt la inceput :incrementeaza contorul I

Alternativa : for I in 1 to 1000 loop

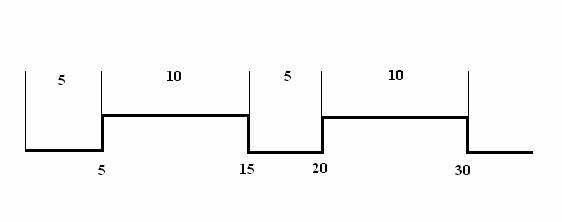

While NOW <15 ns loop

Now: variabila implicita VHDL:timp curent de simulare foarte utila in test bench procesul genereaza un clock continuu (0 15 ns)

Implementarea cu loop:

exit when NOW>=15 ns.

7 LOGICA COMBINATIONALA

Reguli de sinteza pentru logica combinationala :

sensitivity list trebuie sa fie completa( toate intrarile sa fie trecute in ea) ;

nu trebuie sa existe reactii in codul scris in corpul procesului;

nu trebuie sa existe asignari incomplete pentru case,if (orice iesire trebuie sa fie asignata pentru toate seturile de intrari posibile) ;

Exemple ce se abat de la regulile de sinteza pentru logica combinationala :

stimulii si sinteza dau reactii diferite.

Analiza de timp,optimizarile,(sinteza nu e buna).

Ce sunt latch transpuse in logica combinationala.

De aici se trage concluzia unui proces oricat de lung si complicat,cu utilizare de instructii ;nu exista limita pentru structurile incuibate.

Procesul este sintetizat ca logica combinationala fara latch :bistabile.

8 PROCESE ECHIVALENTE

Se refera in special la asignarea de semnale concurente.Ex. 25 Asignarea este validata de un eveniment

(after .ns) proces echivalent.AB<=A and B after 2 ns ;

Si-ul definit de procesul de la ex.26 poate fi utilizat ca si componenta pentru a crea ex.25

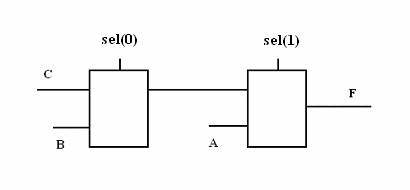

Asignare de semnale conditionate

[

Ex. In care se foloseste un process:

begin

if S0='1' then

F<=A;

elsif S1='1' then

F<=B;

Else

F<=C;

end if;

end process;

Concluzie:

Asignarea conditionata este de multe ori o solutie mai buna pentru a descrie si sintetiza logica combinationala.