|

|

|

ELECTRONICA SI TELECOMUNICATII

VLSI

Isi propune familiarizarea studentului cu uneltele de lucru oferite de mediul Xilinx WEB Pack avand ca scop :

1. sinteza unor fisiere VHDL deja create

2. simularea cu ajutorul fisierelor test bench

3. implentarea in FPGA

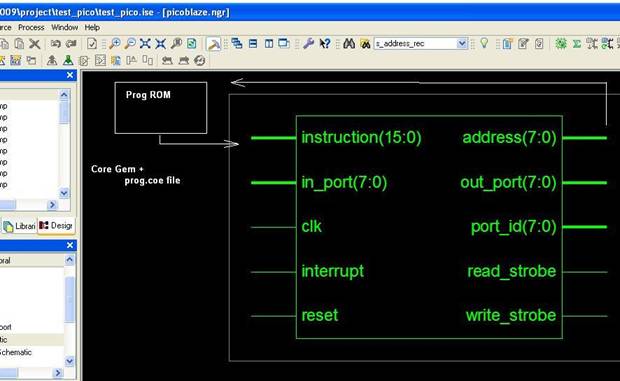

Pentru exercitiul de mai sus s-au ales fisierele sursa ale unui microprocessor PicoBlaze,iar pentru

-> simulare vom folosii un fisier test bench waveform,

->pentru aplicatia de implementat in FPGA vom folosii un IP,care simuleaza o memorie de unde vom citi instructiunile necesare.

Sinteza VHDL

Limbajul VHDL a fost mai intai dezvoltat ca limbaj de descriere si simulare a circuitelor si abia mai tarziu acest limbaj a fost adaptat pentru sinteza. Astfel ca limbajul are multe caracteristici si constructii care nu pot fi sintetizate. Subsetul de instructiuni si programe prezentate in aceasta sectiune sunt sintetizabile majoritatea.

Trebuie de retinut ca modul in care este descris un circuit in VHDL, se rasfrange asupra "calitati" circuitului sintetizat, in continuare sunt prezentate cateva recomandari:

- Structurile de control seriale de tipul if-elsif-elsif-else pot fi sintetizate sub forma unui lant serial de porti logice, ceea ce favorizeaza intarzierile, astfel ca in acest caz este mai bine sa se foloseasca instructiunile de selectie case sau with daca conditiile se exclud reciproc.

- In cazul in care se folosesc instructiuni conditionale in cadrul unui proces, daca pentru o anumita combinatie a intrarilor se omite specificarea valori pe care

trebuie sa o ia aiba iesirea, compilatorul va crea un latch la iesire care sa poata pastra vechea valoare a semnalului de iesire care altfel ar trebui sa se schimbe.

In general generarea unui astfel de latch nu este dorita.

- Instructiunile de ciclare creeaza in general copii multiple ale logicii combinationale descrise in cadrul instructiunii. Daca se doreste folosirea unei singure astfel copii a logici combinationale intr-o secventa de pasi atunci trebuie sa se proiecteze un circuit secvential.

Este posibil ca sinteza unor constructii si structuri ale limbajului sa nu fie posibila cu anumite programe de sinteza, pentru aceasta trebuie consultata documentatia respectivelor programe pentru a vedea ce este si ce nu este sintetizabil.

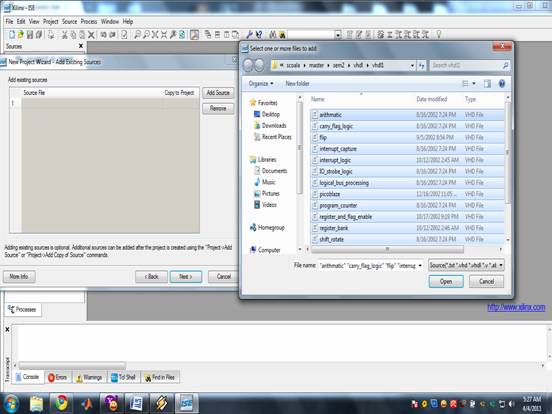

Se deschide mediul ISE,si se alege New Project,dupa ce se salveaza cu numele dorit si in folderol dorit,se alege optiunea add sources ,si aleg surcele microprocesorului PicoBlaze,apoi se apasa next.

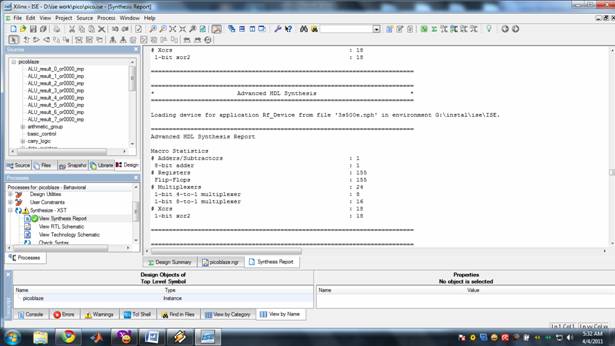

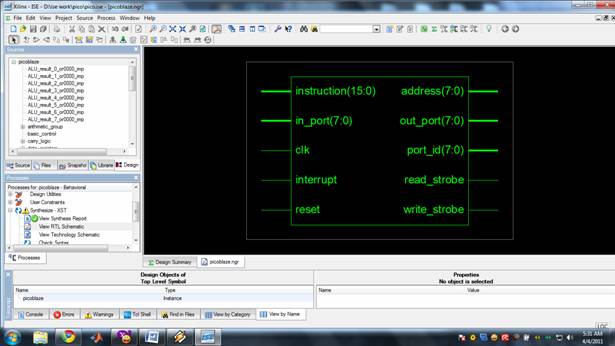

Se alege apoi Implement top module,iar daca alegem Synthesys XST

Putem vedea raportul de sinteza, schema RTL,verifica erorile de syntaxa sau genera un model de simulare post sinteza..

Simularea VHDL

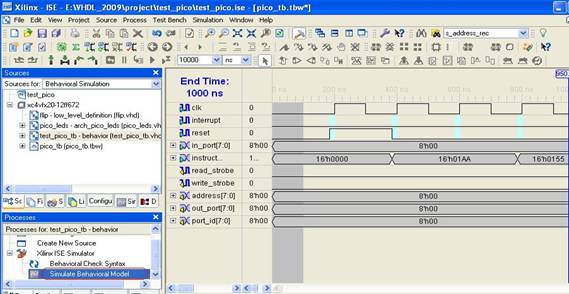

Se ataseaza

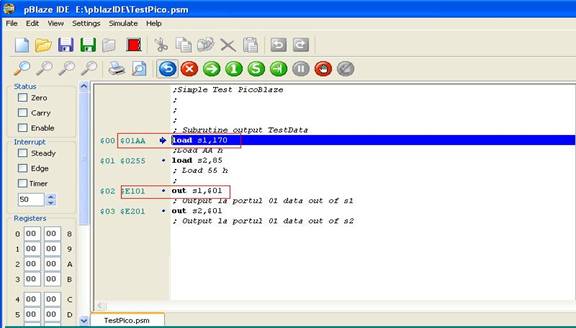

Test Bench Waveform (Xilix simulator) cere un clk - se lasa 100 ns si toate setarile Initiale (nu conteaza!). Apoi se seteaza In Waveform la intrarile Instruction - Instructiile luate din pBlazeIDE.

Fiecare instructie are nevoie de 2 DOUA tacte sa fie executata. Setati deci pe interfata grafica de vectori de test noi instructii de 16 biti din doua in doua tacte!

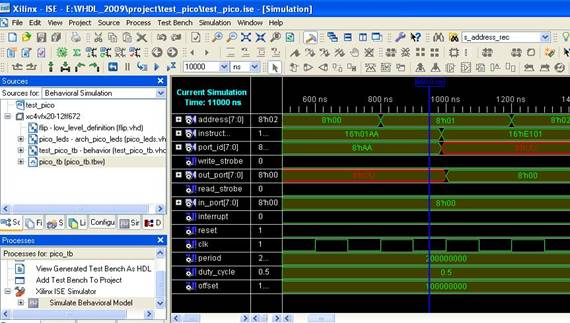

O data creat sistemul de test cu Micro si

Waveform se selecteaza Pico si se lanseaza Fereastra - Behavioral Simulation pornind din Implementation

Nota: Instructiile se pun pe magistrala de date din trei in trei tacte sa fie 'acceptate' la final de Load in ciclul de executie de doua tact.

IP CORE

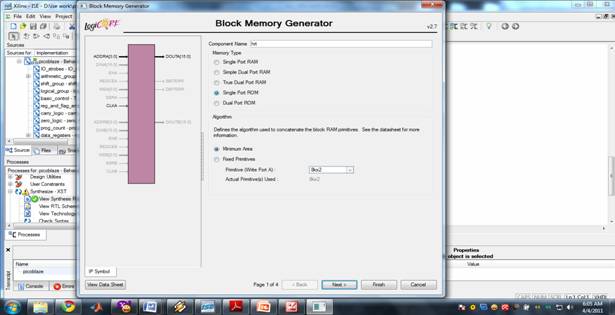

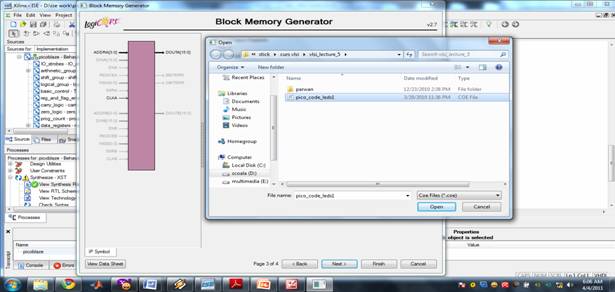

Se da click dreapta pe top-module si se alege new source ,iar din meniul aparut alegem IP core generator,pentru aplicatia curenta vom genera un bloc de memorie pe care o vom initialize cu instructiunile din PicoIDE.

Putem alege tipul de memorie dorit,latimea minima

,lungimea,nu avem nevoie decat de o memorie simpla ROM din care sa citim,se

apasa next iar in dreptul instructiuni initialization file se alege fisierul de

tip coe care contine instructiunile,in

fisierul top module se adauga componenta de memorie si se fac maparile

necesare.

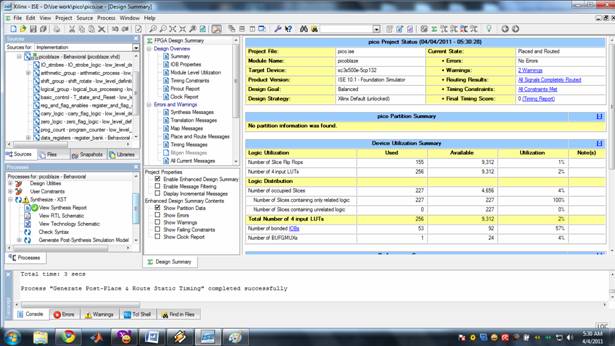

Implementarea in FPGA

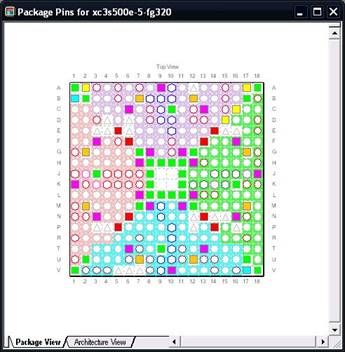

Pentru implementarea in FPGA vom folosii o IP core generator pentru a genera un block de memorie,din care vom citii instructiunile necesare aplicatiei.urmatorul pas e setarea constangerilor.In fereastra Processes (stanga-jos) se selecteaza optiunea Floorplan IO - Pre-Synthesys. Fie se face dublu clic, fie se face clic dreapta si se alege optiunea Run.

ISE

lanseaza utilitarul Xilinx PACE.

![]()

In fereastra aparuta, la mijloc-jos se

apasa tabul Package View ce ne permite sa vedem

configuratia pinilor FPGA-ului folosit.

Dintre cele 8 LED-uri disponibile pe placa, alegem LED-ul LD0, care e legat la pinul J14.

Se face File/ Save, se alege optiunea implicita (XST Default: <>). Se inchide fereastra Xilinx PACE si se revine in programul ISE

Din meniul Process se alege optiunea Implement Top Module. Se lanseaza in executie implementarea - sintetiza proiectul in cipul FPGA - Spartan 3E. Dupa incheierea procesului de implementare, in fereastra Process (stanga jos), liniile Synthesize - XST si Implement Design trebuie sa fie marcate cu o bifare de reusita de culoare verde.

Se genereaza fisierul de configurare al integratului Spartan. In fereastra Process (stanga jos) se face sublu clic (sau clic dreapta - Run) pe linia Generate Programing File:

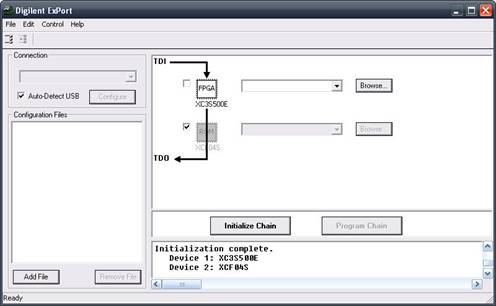

Se stabileste legatura calculatorului cu placa Nexys2 prin intermediul cablului USB. Se porneste alimentarea placii prin comutarea butonului de Pornit/Oprit de pe placa.

Se porneste programul Adept: Start/Programs/Digilent/Adept/ExPort, sau se face dublu clic pe ichonita ExPort de pe desktop.

Se face initializarea circuitului de programare prin apasarea butonului Initialize Chain.Se bifeaza memoria XCF04S, care este o memorie Platform Flash si pe care nu dorim sa o programam. Prin aceasta bifare, memoria XCF04S este scoasa din lantul de programare.

Cu Browse se merge in directorul Student/SLP/and_gate2 si se alege fisierul de tip .bit care contine informatia de configurare a FPGA-ului si care a fost generat .

Se apasa OK la informarea de atentionarea legata de tactul de programare.

Se apasa butonul Program Chain si se asteapta informarea de programare reusita.

Pe placa Nexys2 LED-ul portocaliu DONE trebuie sa lumineze, indicand programarea FPGA-ului

Concluzii

Acest proiect prin intermediul celor trei etape :

sinteza

simulare

implemtare in FPGA,

folosind mediul de dezvoltare Xilinx ISE a oferit posibilitatea dezvoltarii unei aplicatii pentru microprocessor-ului 8 bit RISC PicoBlaze si intelegeri functionarii acestuia.