|

|

|

TIPURI LOGICE

Exista doua tipuri diferite in pachetul STANDARD pentru a reprezenta un bit de informatie :

1. Type BOOLEAN utilizat pentru conditionari in :if,while,exit si next ,sintetizat in final printr-un fir.

Bit BOOLEAN Type (type bit) :reprezinta o restrangere la valori limitate teoretice '0' si '1'si nu contin stari nedeterminate sau inalta impedanta.Se recomanda STD_LOGIC pentru sinteza.

2. Type STD_ULOGIC ('u','x','0','1','z','w','l','h','-'

Pentru a descrie proiecte logice in VHDL sunt necesare operatii booleene :exista 7 operatori logici care opereaza asupra a 5 tipuri:

Operatori logici:and nand

or nor

xor xnor

not

Types(tipuri): BOOLEAN

BIT BIT_VECTOR

STD_LOGIC STD_LOGIC_VECTOR

ex:

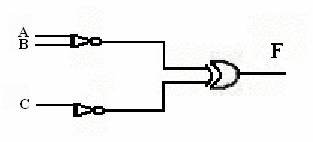

signal A,B,C: STD_LOGIC ;

F<=(A nand B)xor(not C);

Observatie: cu toate ca STD_LOGIC are 9 valori ,la sinteza apare o singura legatura electrica(fir),nu 4 fire.Explicatia este urmatoarea:STD_LOGIC este un tip intern tratat special prin functia RESOLVED.

Exercitiu: signal A,B:STD_LOGIC;

(A='0')or(B='0') ce tip rezulta din aceasta expresie?

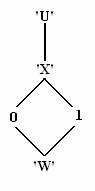

STD_LOGIC 'X' si 'W'-necunoscut

strong 'X' Weak: ;W', 'L', 'H'

WEAK:modele pull up,0h outputs,memorari cu capacitati ,orice situatie unde exista WEAK driving strength.

'U'-neinitializat bit inainte de initializare are o valoare cunoscuta;'U','X','W':nu apar in sintaxa!

Obiectele signal :

'X' la erori,ex.:conflict bus ;2 iesiri logice se leaga impreuna.

'W' :terminator de bus cand bus nu este utilizat;

'Z':inalta impedanta;

-:nu conteaza(dummy) ;la sinteza permite o buna optimizare.

Ex.4 :- e folosit pentru a optimiza circuitul la sinteza cu un numar redus de porti logice.

Ex.5 :- nu este folosit ca input.

Ex.6 :'z' tristate driver ;

Cand un semnal este asignat intr-un proces,procesul este un driver VHDL pentru semnal.Daca valoarea driverelor este diferita,poate avea loc un conflict,dar nu in acest caz.

Diferente intre : STD_LOGIC si STD_ULOGIC(subtype) :

Au aceleasi valori si operatori.Diferenta consta in :STD_LOGIC include functia resolveitcare este apelata imediat de simulator pentru a calcula valoarea semnalului din valorile livrate de drivere.

Function Resolved

(S :STD_VLOGIC_VECTOR)

return STD_VLOGIC ;

Subtype STD_LOGIC is

Resolved STD_VLOGIC;

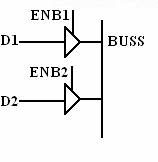

Cand un signal este asignat ca Buss,face ca simulatorul sa treaca valorile livrate de cele doua drivere prin functia RESOLVED care returneaza o valoare pentru semnal.

Buss<=D1; Buss<=D2;

('0' '1')

Resolved('0','1');

'-','0','1'=>'x'

'L','H'=>'W'

in alte combinatii invinge valoarea strong ('0' ,'1' ,'x')

VALORI INITIALE

Pentru semnale,initializarea variabilelor la startarea simularii depinde de tip si este prima valoare din lista.(implicit).

Initializare: S=ADD la ex.1

Type STD_VLOGIC is ('U',.)

Clock,reset:='U' , V:="UU";

Initializare explicita (:= __initializare )

La ex.1,Signal S:OPCODE:=Halt;

Variable V:STD_LOGIC_VECTOR(0 to 1):="00"

:= initializare pentru orice obiecte signal,variabile.Initializarile au loc numai la start simulare.

Nota :initializarea este ignorata de sinteza automatelor,ea fiind respectata doar in cadrul simularii.

De aici rezulta initializarea obiectelor pentru test bench,dar pentru RTL trebuie utilizat explicit un semnal de reset pentru .initializare care poate adduce variabilele intr-o stare cunoscuta..

CONSTANTE

Sintaxa :

Constant new_name :Data Type :=Expresie ;

Constanta are obligatoriu o valoare initiala care va ramane constanta in timpul simularii.

NU poate fi asignata!

In ex.10: "0000"-rangul este dedus din rangul valotilor initializate.

CONCATENARE

Utilizeaza operatorul '&'pentru a lega impreuna caractere si arii , pentru a creea arii mai mari.

Vezi ex.11.

Vectori

F(15)=A(7) F(8)=A(0) F(7)=B(7) F(0)=B(0)

Exemplul 12:

Vectori + biti

F(3 downto 1)<=(A&B)&C; F(3)=A ;F(2)=B ;F(1)=C ;F(0)=neschimbat

Operatii de deplasare(shift) si rotire

Combina concatenarea cu parti de vector

Deplasare stanga cu un pas ;

Rotire stanga cu un pas ;

Operatori:

Shift left logic(sll) shift right logic(srl)

Shift left arithmetic(sla)shift right arithmetic(sra)

Rotate left(rol) Rotate right(ror)

Reg<=reg sll 1;

Reg<=reg rol 1;

Test : variabila A:STD_LOGIC_VECTOR(3 downto 0);

..

A:="0110";

Evaluati A(0) '1' , A(2 downto 1):"0111".

OPERATORI OVERLOADING (supraincarcare)

Implicit definit in VHDL pentru a aduna intregi sau vectori in VHDL in pachetul IEEE.STD_LOGIC_1164.all;

In acest pachet exista Type STD_LOGIC_VECTOR cu 7 operatori.

Definirea de operatori pentru a lucra intr-un nou tip este numita operator overloading.Exista operatori definiti implicit pentru toate tipurile.

Operatori relationali

STD_LOGIC_VECTOR > ;>= ; < ; <= ; = ; /= ;

"+"nu exista definit in 1164,dar poate fi definit pentru STD_LOGIC_VECTOR si pus intr-un pachet.

In sinteza VHDL exista un package care adauga cativa operatori aritmetici la STD_LOGIC_VECTOR sau la altele.

Ex.14 : Use COMPASS.LIB.COMPASS.ALL;

Alta varianta in ex.15:

Use IEEE.NUMERIC_STD.ALL;(include signal,unsignal,array,type)

A,B,SUM:definite fara semn..

FUNCTII DE CONVERSIE

Ex.16 se utilizeaza IEEE.NUMERIC_STD.all

Proces=codificator de prioritate:selecteaza pozitia cu cel mai din stanga,1 in vectorul A

F-unsigned vector,F:asignare ilegala.

A="00000001" F="000"

A="11100000" F="111"

Solutie:o functie explicita de conversie pentru a converti o valoare dintr-un tip in alt tip.Sunt introduse functii de conversie,date in pachete de sinteza.

Ex :IEEE standard 1076.3. F<=To_unsigned(I,3) ;converteste un intreg intr-un unsigned.

Parametrii in :I-are valoare de conversie(valoarea tip intreg de convertit) ;3-are valoare de bit

Ex.17 To_integer(S): converteste S in intreg.Este definita doar in IEEE.NUMERIC_STD.all.