|

|

|

Acest capitol se ocupa cu introducerea in VHDL si sinteza VHDL si explica cum acestea pot

fi utilizate impreuna la proiectarea hardware.

Scop :

Ce este VHDL si la ce se poate utiliza ?

Cum este utilizata sinteza la proiectarea automata la nivel de porti logice ?

1.1

1. Ce este VHDL ?

VHDL=VHSICHadrdware Description Language ;VHSIC=Very High Speed Integrated Circuit.

Proiect sponsorizat de Guvernul USA si Air Force incepand din 1980,pentru tehnici automate de proiectare a VCSI chips.

VHDL :dezvoltat pentru a asigura un format standard pentru manipularea unui volum mare de date pentru proiectarea hard.

2.VHDL este un limbaj utilizat pentru a descrie structura si comportarea sistemelor hard.

VHDL :definit precis si complet de Language Reference Manual(LRM).

VHDL este inclus in alte limbaje de nivel inalt.

3.Scule (unelte sau Tools-uri,in engleza,tools=unelte) :esentiale pentru proiecte de nivel

inalt. Ex :

1.simulator ;

2.sinteza ;

LRM defineste ce trebuie sa faca un simulator VHDL.

4.VHDL nu impune prin standard un stil de descriere,de programare hard,stilul se

formeaza utilizand exemple si proiecte mici care ne invata sa renuntam la stilul

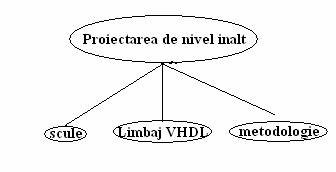

de proiectare la nivel de porti logice si sa adoptam stilul la nivel de functiuni.Succesul proiectarii de nivel inalt necesita :

a) limbaj ;

b) unelte(tools) ;

c) metode :experienta,educatie ;

1.2 Istoria VHDL : a inceput in 1981 la nivelul departamentului apararii militare SUA.

1985 :Basic VHDL(versiune nepublica).In 1987 s-a pus problema standardizarii VHDL.

1993 :s-a facut public sub standardul IEEE;

1995 :apare varianta de simulare acceptata;

1996 :tools-uri specifice pentru sinteza automata;

Incepand de aici,la fiecare cinci ani standardul se reinnoieste(se face o revizie)

1.3 Implicatii ale utilizarii VHDL :

La nivelul proiectantului hard :proiectarea de nivel inalt abstract,utilizand unelte,metode complet noi in procesul de proiectare.

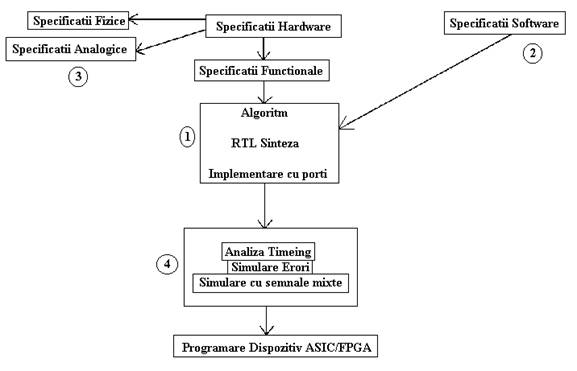

Metodologia de utilizare VHDL (ce poate sa faca VHDL)

Analiza si partitionarea sistemului utilizand VHDL

Etape :

Scrie cod VHDL pe blocuri functionale ;

Scrie cod pentru test bench ;

Sunt introduse in simulator VHDL;

Sinteza cu porti logice in mod automat ;

Simulare cu porti ;

Programare dispozitiv final(FPGA,ASIC) :dispozitive finale ;

Test fizic :daca nu suntem multumiti mai putem face modificari la nivel de cod ;

FPGA=field programable gate array;

ASIC=application specific integrated circuit;

Avantaje ale structurii de mai sus :

Creste productivitatea proiectarii ;

Se face o testare prin simulare inainte de sinteza ;

Sinteza cu porti se face automat :implementarea se bazeaza pe descrierea la nivel inalt ;

=>Utilizarea VHDL eficienta :

Invat sintaxa VHDL ;

Invat stil de programare prin exemple ce duc la o sinteza automata eficienta ;

In cadrul blocului 1 se utilizeaza VHDL.Blocul 2 se refera la limbaj(tot la VHDL).

Dezavantajele limbajului VHDL :

VHDL este focalizat asupra functionabilitatii sistemului,cu referire la hardware numeric.

Exista medii noi de VHDL ce pot simula circuite analogice (functiuni) :Analog VHDL(IEEE standard).

Blocul 3 modeleaza CAN.Blocul 4 apare intr-un mediu VITAL=VHDL Initiative Towards ASIC Libraries.

Nivele de abstractizare

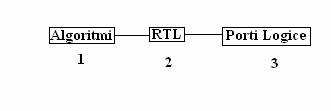

VHDL poate fi utilizat pentru a descrie hardware-ul pe mai multe nivele de abstractizare.Pentru aplicatii VHDL cu implementare ASIC, uzual utilizeaza 3 nivele:

La nivelul pasului 1(Algoritmul),nu exista sinteza.Apare o sinteza la nivel inalt cand trec de la Algoritm la RTL si o RTL sinteza dupa aceea.

Diferentele intre nivele se refera la termeni privind Timeing-ul.

1.Algoritmul pur :consta intr-un set de instructii ce sunt executate secvential in scopul rezolvarii

unui task.Nu exista clock-uri si temporizari.

Aspecte de time-ing pot fi inserate fortat in secventa de operatii.

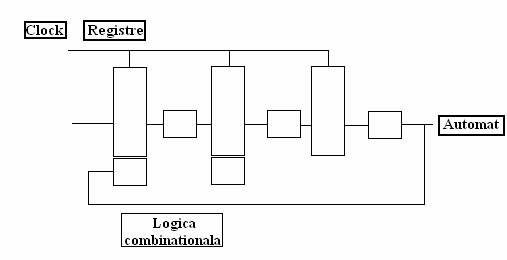

2.RTL=register transfer logic,are un clock explicit;toate operatiile vor fi gestionate si se executa

sincron cu acest clock.Nu exista detaliate intarzieri sub nivel de ciclu(tact).

3.Porti logice :prezinta o descriere generata automat,consta intr-o retea de porti + registre care apartin unei biblioteci tehnologice care contine specificatii tehnologice ale circuitului programabil final:ASIC/FPGA:functiuni logice(porti,registre)+intarzieri specifice circuitului ales:exista clock.

1.6 Ce este sinteza ?

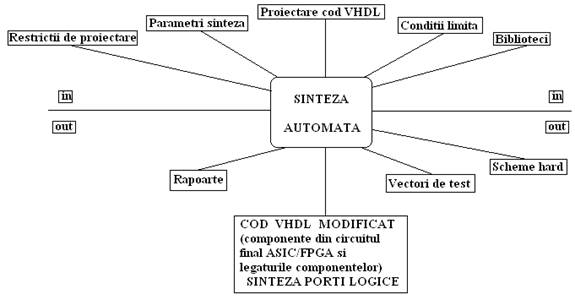

Sinteza se refera la generarea de structuri logice hard plecand de la descrierea de nivel inalt VHDL.Ea genereaza cod modificat VHDL in scopul optimizarii implementarii in resursele fizice finale : ASIC/FPGA.

Figura prezinta intrarile si iesirile unei structuri tipice de sinteza.

Biblioteci(IN) :specifica caracteristicile :structura si comportarea circuitului final ASIC/FPGA ;contine o descriere functionala si caracteristicile electrice ale celulelor,componentelor din cipul final.

Bibliotecile includ :porti logice simple,bistabile ,functii multibit.

Intrari in sinteza :

Restrictii de proiectare :frecventa maxima de clock.

Conditii limita : fan out.

Parametrii de sinteza :ciclul minim de calcul pentru o unitate centrala.

Iesiri din sinteza :

Rapoarte :procentul de utilizare al circuitului,restrictii ce nu s-au putut realiza,recomandari .

Vectorii de test :se genereaza automat la nivel de sinteza.

Pentru ca in circuitul final sa am posibilitati de testare e necesar sa sciu cod VHDL pentru Functiuni de testare :pini dedicati numai pentru testare.Dupa sinteza automata,la acest nivel se utilizeaza simularea care da informatii si de viteza de executie,de densitatea circuitelor utilizate in cipul final.

Rezultatele de simulare le interpretez si optimizez codul VHDL.

De la fiecare proiect ,prin simulare si optimizare de cod castig experienta in a scrie codul optimizat.

1.7.Ce este RTL-sinteza ?

In VHDL, RTL descrie explicit sincronizarea tuturor operatiilor cu un clock.(inlatura hazardul)

Esenta RTL :consta in definirea de registre si ca transferul intre acestea e sincronizat cu un clock.

Aceasta parte a RTL sinteza e un automat cu stari finite.

In esenta, RTL optimizeaza logica combinationala.

1.8. ASIC si FPGA (circuitele finale ce se implementeaza)

Finalitatea proiectarii in VHDL e sinteza logica cu arii de porti si celule standard inglobate in ASIC/FPGA si PLD complexe.Limbajul VHDL este utilizat pentru ambele ASIC si FPGA dar, exista recomandari pentru scriere de cod pentru un tip ce difera fata de celalalt.

Recomandari cod pentru implementare cu ASIC

Are in vedere o buna descriere la nivel RTL:sinteza opyimizeaza legaturile combinationale in scopul de a exploata tipul de celule disponibile in tehnologia ASIC.

Recomandari pentru FPGA

Codul VHDL se scrie optimizat in vederea exploatarii directe a arhitecturii si al specificului celulelor din FPGA.La FPGA exista un fan in mai scazut.

Recomandari specifice vor fi evidentiate in cadrul capitolelor finale din curs.

1.9.VHDL in lume

Standarde IEEE legate de VHDL

Standardul 1029.1 :WAVESdefineste vectorii de test si vectorii de unda in VHDL.

Standardul 1076 :se refera la VHDL language reference manual,manual ce are mai multe capitole de interes:

1.Referinte analogice;

2.Mathematic Package;

3.Pachet de sinteza;

4.Metode de timeing(Timeing Methods-VITM);

5.Biblioteci utilitare (Utility Libraries) ;

Standardul 1164:se refera la sisteme logice multinivel si adauga modele practice si exemple de cod.

Organizatii :

In 1991 : se infiinteaza VHDL International ;se infiinteaza alta organizatie :ECSI(European Code Standardisation Initiative) ;

Users

Groups :

Internet:http://VHDL.work ->homepage