|

|

|

PROCESE SI SINCRONIZARI

Procesele :principala modalitate in descrierea VHDL.Capitolul arata cum sunt executate

procesele de simulator si cum pot fi utilizate la proiectarea si sinteza hardware.

Fiecare proces are alocat un calculator!

Definitie: Procesele sunt structuri concurente;corpul lor se executa secvential.

Un proces se activeaza sub controlul unei liste de senzitivitate.In cadrul procesului pot

exista stari WAIT,caz in care executia secventiala a procesului se opreste la intalnirea

unei stari WAIT si se continua dupa temporizarea(delay-ul) prescrisa de WAIT.

Cand cel putin o variabila din lista de senzitivitate isi modifica starea logica,corpul

ruleaza pana la sfarsit.

Sintaxa :

[eticheta :] process[(lista sensitivity)]

declaratii de tip.

begin

corpul procesului(executie secventiala)

end process [eticheta :] ;

Procesele sunt utilizate pentru a descrie parti de functiuni din sistem, fara a intra in detalii de implementare,deci se pot descrie hardware la un nivel inalt de abstractizare.Se pot descrie vectori de test.

Procese=structuri concurente scrise in cadrul unei arhitecturi.Fiind structuri concurente,procesele

se executa paralel.Orice proces descrie separat o parte hardware sau un task autonom,concurent

cu alte task-uri

Un proces il putem vedea rulat pe un calculator dintr-un sistem mmultiprocesor.In corpul procesului,se executa secvential intre begin si end.

2 LISTA DE SENZITIVITATE

Este o lista de semnale ce apare in paranteza dupa proces.Procesele se activeaza cand

apare un eveniment la unul din semnalele din lista(sa-si modifice starea).La eveniment,se executa tot corpul,pana se ajunge la end.

Pentru exemplul 2,semnalul mask nu face parte din lista de senzitivitate.Cand apare un eveniment,(schimb de stare) pentru mask,acest proces nu se ruleaza pentru ca mask nu apartine listei de senzitivitate. eroare.Daca apare un eveniment la C,procesul se ruleaza,chiard aca in corpul procesului nu se utilizeaza C.

Concluzie : lista de senzitivitate contine un set de semnale la care procesul este senzitiv

si nu neaparat intrari in proces :exemplu Cpoate fi o intrare de sincronizare

Nota :procesele utilizate in sinteza functiunilor logice combinationale trebuie sa aiba

lista de senzitivitate completa(toate intrarile sa apartina listei).Daca lipseste o

intrare din lista,procesul nu va recalcula iesirea cand intrarea in lista va schimba in

stare.

3 STARI WAIT

Corpul procesului contine 1.n stari wait.Procesul incepe executia la timpul 0,apoi se suspenda pe intreaga durata a starii wait precizata de wait.

Cand procesul a ajuns la end,reia pornirea (start-ul)executiei de la inceput.

Pe durata suspendarii procesului,alte procese se pot executa (vezi concurenta proceselor).Acest tip de proces este folosit pentru a genera vectori de test ,dar nu pentru a descrie hard in RTL.Exista wait fara parametru!Procesele fara wait se executa intr-o bucla infinita.Atentie !!!

Acest tip de proces este de cele mai multe ori cea mai buna cale de a genera vectori de test in test bench.In practica,procesul pentru test bench este mult mai complex,dar principiul de baza este acelasi cu etapele :

1.Aplica o parte vectori ;

2.Asteapta un interval de timp precizat;

aplica alta parte vectori ;

4.asteapta un timp precizat ;

etc

4 ASIGNARI DE SEMNALE IN PROCESE

Asignarile de semnale sunt utile pentru a crea evenimente asupra semnalelor si permit in acest fel comunicarea intre procese (ordinea de executie este de la ultimul proces la primul).

Nota :in cadrul proceselor,asignarea este secventiala pe cand in cadrul arhitecturilor asignarea este concurenta.

Sintaxa:[label:]nume_signal<=Expresie[after delay];

Expresie[....];

....

unde Expresie descrie o operatie logica sau aritmetica.

In continuare se studiaza evolutia unui proces pentru a vedea exact ce se intampla:

B startbegin

secventa

end

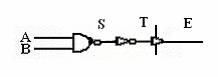

Calculeaza A*B apoi pregateste evenimentul S sa apara in viitor dupa 2 ns.

Nota:asignarea nu schimba valoarea semnalului.

Executia procesului :

1.Presupunem ca B schimba de stare.Va executa corpul pana la end.Se calculeaza A si B,se selecteaza evenimentul S !(nu se activeaza ca sa apara in viitor dupa 2 ns).

Pentru instructiile care urmeaza secvential,se va lucra cu vechea valoare.Nu se va programa un eveniment pentru S sau T.

Se atinge end :procesul se suspenda si asteapta un eveniment(schimbare de stare la un semnal din lista de senzitivitate).Dupa 2 ns apare un eveniment si S isi schimba valoarea logica.

2. Procesul se executa pentru ca apare o schimbare in S,care apartine listei de senzitivitate.Prima asignare nu are efect(A si B nu se modifica).A doua asignare programeaza un eveniment T fara delay,dar nu schimba valoarea lui T !(important).A treia asignare nu are efect pentru ca T pastreaza vechea valoare.Se ajunge la end.

Cand toate procesele active la momentul curent au terminat executia la timpul curent, simulatorul analizeaza evenimentele din lista de senzitivitate.Pentru ex.5,T schimba de stare.

Mica intarziere asociata evenimentului T se numeste delta delay.

Procesul S se executa a treia oara.

S si T sunt fara efect,F este programat ca eveniment dupa 1 ns.Cand F schimba de stare,procesul nu se executa deoarece F nu apartine listei de senzitivitate.

Obisnuit,delayurile asociate lui after nu se includ in sinteza,ele sunt utilizate in simulare pentru a simula la acest nivel delay-uri ce depind de tehnologia finala de implementare.

Reguli pentru sinteza logicii combinationale cu procese:

1. Lista de senzitivitate trebuie sa includa obligatoriu toate intrarile ;

2. Iesirile trebuie sa depinda doar de intrari (fara reactii) ;

In cazul folosirii structurii if-chase,structurile trebuie sa fie complete(sa nu lase o ramura fara actiune).

Exemplul 6 nu respecta regula a 2-a deoarece are reactie.

feedback: process(S,R,Q,QB)

begin

.....

Unele programe(tool) de sinteza accepta acelasi cod. Probleme sunt posibile sa apara la optimizare sinteza crede ca este vorba despre un circuit combinational si nu intelege comportarea secventiala a acestui bistabil.Solutia acestei probleme ramane ca tema.