|

|

|

DECODIFICATORUL (DCD)

Functie Serveste la identificarea unui cod de intrare cu n biti prin activarea unei singure iesiri (din cele m) corespunde codului de intrare. Fiecare iesire corespunde unei anumite combinatii a valorilor de intrare. In general intre n si m exista relatia m = 2 n, dar exista si DCD la care m < 2n.

In schema bloc din figura 10., vectorul intrarilor este format din cele n linii notate x0, x1, xn-1, iar vectorul iesirilor (active SUS in varianta a, respectiv active JOS in varianta b) din liniile y0, y1, , ym-1. En este o intrare

de validare care poate inhiba simultan toate iesirile DCD. In tehnologie CMOS, in seria 4000 iesirile DCD disponibile sunt fie active SUS, fie active JOS, iar in tehnologie TTL (implicit si in seriile CMOS rapide 74HC, 74LV, etc) iesirile DCD sunt active JOS.

a. b.

Figura 10. Schema bloc pentru un decodificator n:m cu validare,

a - iesirile active SUS, b - iesirile active JOS.

Cel mai simplu DCD are o intrare si o iesire, fiind realizat cu un inversor (figura 11). Un DCD 2:4 necesita 4 porti SI-NU si doua inversoare, iesirile fiind active JOS.

a) b)

Figura 11. DCD simple - schema electrica,

a - DCD 1:2, iesiri active SUS, b - DCD 2:4, iesiri active JOS.

Schema electrica pentru un DCD 3:8 necesita 8 porti SI-NU cu cate 3 intrari (figura 12). Intrarile se aplica prin perechi de inversoare pentru a asigura ca fiecare intrare sa reprezinte o singura sarcina (TTL).

Schema se poate completa cu un circuit de validare (figura 3.4). Daca circuitul nu este validat, toate iesirile DCD sunt in starea 1. Pentru validare este necesar ca E2 = 1, E1A = E2B = 0.

Figura 12 Structura unui DCD 3:8.

Fiecarei iesiri ii corespunde un circuit SI-NU, ceea ce face ca iesirile circuitului sa fie active pe 0. Acest lucru inseamna ca iesirea activata este pe 0 iar toate celelalte iesiri sunt pe 1.

De exemplu: pentru x0

= 1, x1 = 0, x2 = 1, iesirea![]() este pe 0

si toate celelalte sunt 1.

este pe 0

si toate celelalte sunt 1.

Decodificatorul din figura 13. realizat in tehnologie TTL (74LS138) este foarte raspandit in aplicatii datorita versatilitatii oferite de validarea multipla.

Figura 13. Un DCD 3:8 foarte raspandit, 74LS138

2. Alte tipuri de decodificatoare

Principalele DCD realizate in tehnologie TTL sunt (figura 14):

1. 74LS42 - DCD care serveste pentru decodificarea cifrelor zecimale de la 0,..,9, codificate binar.

Aici m < 2 n (DCD 4:10), fara intrare de validare.

2. 74LS139 - contine doua decodificatoare binare 2:4 complet independente, fiecare decodificator avand n = 2 si m = 4 si are o intrare de validare proprie activa pe 0.

3. 74LS138 - DCD 3:8 contine un DCD 3:8 avand n = 3 si m = 8 si are 3 intrari de validare active pe 0 (2), respectiv pe 1 (o intrare).

4. 74LS154 - decodificator binar avand n = 4 si m = 13 (DCD 4:13).

Figura 14. DCD in tehnologie TTL.

Principalele DCD realizate in tehnologie CMOS sunt (figura 15):

1. 4555 - contine doua DCD 2:4 independente cu iesirile active SUS, fiecare avand n = 2 si m = 4, o intrare de validare proprie activa JOS.

2. 4553 - contine doua DCD 2:4 independente cu iesirile active JOS, fiecare avand n = 2 si m = 4, o intrare de validare proprie activa JOS.

3. 4028 - DCD 4:10 avand n = 4 si m = 10, cu iesiri active SUS fara nici o intrare de validare.

4. 4514 - DCD 4:13 cu iesiri active SUS, intrare de validare activa JOS, avand n = 4 si m = 13.

5. 4515 - DCD 4:13 cu iesiri si intrare de validare active JOS, avand n = 4 si m = 13.

Figura 15. DCD in tehnologie CMOS.

O categorie aparte de decodificatoare sunt utilizate pentru comanda afisajelor cu 7 segmente (figura 16). In tehnologie CMOS se fabrica circuitele 4511 si 4513, cu 4 intrari si 7 iesiri, iar in tehnologie TTL se produc circuite pereche (74LS47 si 74LS247 pentru afisaje cu anod comun, respectiv 74LS48 si 74LS248 pentru circuite cu catod comun):

1. 4511 este un latch, decodificator si etaj de iesire capabil sa furnizeze la iesire un curent de 25 mA, potrivit pentru comanda afisajelor cu catod comun (LED). Poate afisa doar cifrele 09, pe care le poate si memora de altfel.

2. 4543 este un latch, decodificator si etaj de iesire capabil sa furnizeze la iesire un curent de 25 mA, potrivit pentru comanda afisajelor cu catod comun (LED), daca PH = 1 logic, a afisajelor cu anod comun (LED), daca PH = 0 logic, respectiv a afisajelor cu cristale lichide (LCD). Poate afisa doar cifrele 09, pe care le poate si memora de altfel.

3. 74LS47 si 74LS247 sunt decodificatoare realizate pentru comanda afisajelor cu anod comun, care pot afisa 13 combinatii (cifrele 09 si alte 5 semne, plus afisaj stins).

4. 74LS48 si 74LS248 sunt decodificatoare realizate pentru comanda afisajelor cu catod comun, care pot afisa 13 combinatii (cifrele 09 si alte 5 semne, plus afisaj stins).

Figura 16. DCD binar - 7 segmente.

2.1 Extinderea capacitatii de decodificare

Extinderea capacitatii este una din cele mai comune probleme din aria de utilizare a circuitelor integrate digitale, aplicabila practic la toate tipurile de circuite logice: decodificatoare, codificatoare, multiplexoare, numaratoare, memorii, etc. Pentru decodificatoare extinderea tipica se realizeaza dupa schema din figura 17, in care U4A este utilizat pentru validarea unui singur DCD dintre U0 - U3, in functie de combinatia variabilelor x4, x3.

Figura 17. Obtinerea unui DCD 5:32 cu validare.

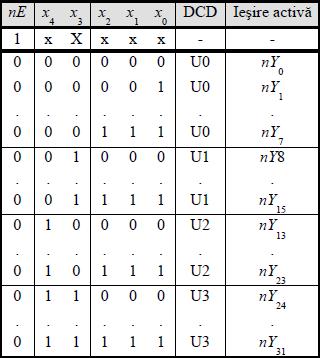

Combinatiile variabilelor x4 - x0 sunt prezentate in tabelul 3.1. nEN este o intrare globala de validare; pentru nEN = 1, toate iesirile sunt inactive (1 logic). De obicei x4 - x0 sunt biti de adresa, rangurile mai semnificative fiind utilizate pentru selectia decodificatorului activ (x4 - x3 selecteaza U0 - U3), iar rangurile mai putin semnificative o anumita iesire dintr-un DCD (x2 - x0 selecteaza una din cele 8 iesiri ale unui DCD).

Versatilitatea intrarilor de validare de la 74LS138 permite o implementare mai simpla a extinderii (figura 18), prin utilizarea unui circuit inversor si renuntarea la posibilitatea validarii globale.

Tabelul 3.Functionarea DCD 5:32 cu validare

Figura 18. Obtinerea unui DCD 5:32, varianta a II-a.

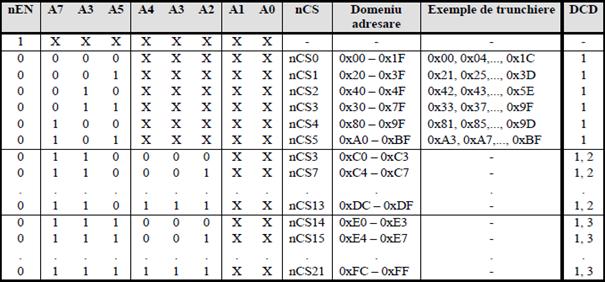

Intr-un microsistem DCD se utilizeaza la selectia diferitelor circuite integrate sau porturi. Un circuit complex (port) poate raspunde la mai multe adrese adiacente (de exemplu circuitul Intel 8255 are o intrare de selectie circuit nCS si doua linii de adresa A0 si A1, continand astfel 4 porturi - 3 de date si unul de comanda).

Decodificarea adreselor

se poate face complet, caz in care toate liniile de adresa

ajung

Figura 19. Decodificarea incompleta a magistralei de adrese intr-un microsistem.

Tabelul 4 Decodificare completa si incompleta cu explicarea spatiului de adresare

2.2 Aplicatii ale decodoficatoarelor

1. Identificarea unui cod - este chiar functia fundamentala a unui DCD.

2. Implementarea functiilor logice (fig.20) cu n variabile, unde n corespunde cu numarul de intrari de cod ale DCD.

Implementarea

functiilor logice folosind DCD este foarte avantajoasa pentru ca

iesirile unui DCD binar reprezinta termenii ![]() din exprimarea

canonica disjunctiva a functiilor logice. Numarul

functiilor (de acelasi numar de variabile binare) ce pot fi

implementate nu este limitat decat de factorul de bransament la

iesire, ce corespunde iesirilor DCD. Exista doua variante

de implementare: DCD si o poarta SI-NU, respectiv un DCD si

o poarta SI.

din exprimarea

canonica disjunctiva a functiilor logice. Numarul

functiilor (de acelasi numar de variabile binare) ce pot fi

implementate nu este limitat decat de factorul de bransament la

iesire, ce corespunde iesirilor DCD. Exista doua variante

de implementare: DCD si o poarta SI-NU, respectiv un DCD si

o poarta SI.

In primul caz la

intrarile circuitului SI-NU se conecteaza iesirile DCD ce

corespund termenilor ![]() cuprinsi in functie.

Pentru a doua varianta, la intrarile circuitului SI se

conecteaza iesirile DCD ce corespund termenilor

cuprinsi in functie.

Pentru a doua varianta, la intrarile circuitului SI se

conecteaza iesirile DCD ce corespund termenilor

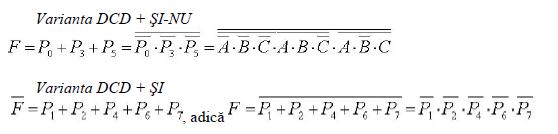

necuprinsi in functia F. Fie functia F = P0 + P3 + P5. In acest caz n = 3 si se poate utiliza un DCD 3:8.

Figura 20. Implementarea de functii cu DCD si porti.

Pentru reducerea numarului de circuite, in cazul functiilor de 3 variabile se utilizeaza varianta cu porti SI-NU pentru functii cu maxim 4 termeni P, iar varianta cu SI atunci cand numarul termenilor care nu apar in functie este mai mic de 4. In tehnologie TTL circuitele SI-NU se fabrica cu 2, 3, 4, 8, 13 intrari, pe cand circuitele SI se fabrica cu 2, 3, 4 intrari.

2.3 Comanda afisajelor cu 7 segmente

Schemele electrice din figurile 18 si 19 sunt evident incomplete,

lipsind rezistoarele de limitare a curentului prin segmente. Acestea se conecteaza in serie cu iesirile DCD si au o valoare tipica de 330Ω. In ambele figuri este redata situatia afisarii semnului corespunzator la 11002 = 0x0C.

Intrarea nLT (Lamp Test) activa JOS determina atunci cand este trecuta in 0 logic aprinderea tuturor segmentelor, permitand astfel verificarea afisajului. nRBI (Ripple Blank Input) este intrarea de mascare a zerourilor nesemnificative, iar nRBO este iesirea corespunzatoare. Pinul nRBO ofera si functia suplimentara

de stergere (BI Blanking Input) prin care se poate comanda stingerea tuturor segmentelor afisajului.

Figura 21. Afisaje cu anod comun comandate de circuitele TTL 74LS47, respectiv 74LS247

Figura 22. Afisaje cu catod comun comandate de circuitele TTL 74LS47, respectiv 74LS247.

Figura 23. Afisaj cu trei cifre - configuratie standard.

Figura 24. Afisaj cu trei cifre - mascarea zeroului semnificativ.

Intrarea RBI permite stingerea zerourilor nesemnificative atunci cand este conectata la iesirea RBO a decodificatorului de rang imediat adiacent.

Figura 25. Afisaj cu trei cifre - testarea segmentelor

Figura 26. Afisaj cu trei cifre cu zero in pozitia cea mai putin semnificativa.

Figura 27. Afisaj cu trei cifre - mascarea zeroului mai putin semnificativ.

Pentru un numar mai mare de cifre comandate se folosesc tehnici de multiplexare a afisarii.

BIBLIOGRAFIE

1. Festila, Lelia - Electronica digitala I - Circuite logice combinationale,

Lito UTCN, Cluj-Napoca, 1994.

2. Festila, Lelia - Electronica digitala I - Circuite logice secventiale, Lito

UTCN, Cluj-Napoca, 1994.

3. Hintea S., Festila Lelia, Cirlugea Mihaela Circuite integrate digitale.

Culegere de probleme. Editura Casa Cartii de Stiinta,

Cluj-Napoca, 2000.