|

|

|

Circuite integrate MOS

Un circuit MOS alimentat la o sursa de curent continuu cu valoarea VCC = 5V are nivele logice limita impuse:

VIHmin = 3,5 V pentru "1" logic,

VILmax = 1,5 V pentru "0" logic.

Producatorii garanteaza la iesirea portii

VOHmin = 4,95 V pentru valoarea minima de "1" logic;

VOLmax = 0,05 V pentru valoarea maxima de "0" logic,

ceea ce determina margini de zgomot

![]() pentru "1" logic,

pentru "1" logic,

![]() pentru "0" logic .

pentru "0" logic .

Nota: De fapt producatorii de circuite MOS spun ca asigura nivele

de tensiune pentru "1" logic ![]() si pentru "0"

logic

si pentru "0"

logic ![]() , dar se poate conta pe 10% din valoarea sursei de

alimentare.

, dar se poate conta pe 10% din valoarea sursei de

alimentare.

Un circuit CMOS alimentat la o sursa de c.c. cu valoarea VCC = 10 V are nivelele limita impuse:

VIHmin = 7,0 V pentru "1" logic,

VILmax = 3,0 V pentru "0" logic.

Un circuit CMOS alimentat la o sursa de c.c. cu valoarea VCC = 15 V are nivelele limita impuse si anume:

VIHmin = 11,0 V pentru "1" logic,

VILmax = 4,0 V pentru "0" logic.

Marginile de zgomot sunt:

![]() ,

,

![]() ,

,

ca in figura 4.13.

Marginea de zgomot este deosebit de importanta in cazul in care semnalele logice sunt formate dintr-un semnal logic curat" peste care se suprapune o tensiune de zgomot. Valorile mari ale zgomotului pot duce semnalul in zona de incertitudine, eventual circuitele pot interpreta un semnal logic drept altul. Spre exemplu in figura 4.14 semnalul de intrare Vi este "1" logic la valoarea de 2,4 V, peste care

s-a suprapus un zgomot cu amplitudinea maxima de 0,9V.

Pe axa timpului, in figura 4.14, este marcata starea iesirii circuitului, care ar trebui sa fie "1" logic, dar datorita perturbatiei semnalul de intrare, se situeaza de doua ori in zona de incertitudine si iesirea are o valoare care nu poate fi precizata ("0" sau "1").

Portile integrate MOS se clasifica pe baza tehnologiei de realizare a tranzistorului unipolar in:

P-MOS, au in componenta tranzistori cu canal P

N-MOS, au in componenta tranzistori cu canal N

C-MOS (Complementary MOS), au in componenta atat tranzistori cu canal P cat si tranzistori cu canal N;

Bi-CMOS (Bipolar CMOS)

Portile PMOS si portile NMOS nu au fost standardizate ci numai intra in componenta unor circuite integrate care implementeaza diferite functii logice.

Tranzistorii MOS cu canal n, utilizati la realizarea portilor NMOS sau (CMOS) se prezinta in figura 4.15, unde avem a) MOS cu canal initial cu saracire si b) MOS cu canal indus cu imbogatire.

Sunt preferati tranzistorii cu canal indus (4.15b) deoarece polaritatea tensiunii de intrare VGS este aceeasi cu polaritatea tensiunii de la iesire VDS.

Caracteristica statica de iesire, din figura 4.16, permite evidentierea regimurilor de functionare ale tranzistorului:

zona de blocare, este caracterizata prin anularea curentului de

drena

(![]() ). Regimul se stabileste pentru tensiuni de intrare mai

mici ca tensiunea de taiere (

). Regimul se stabileste pentru tensiuni de intrare mai

mici ca tensiunea de taiere (![]() ).

).

zona de saturatie, este zona in care curentul de drena (![]() )

)

este comandat de valoarea tensiunii grila - sursa (de la intrare)

![]() ,

,

unde k este o constanta specifica

calitatii realizarii fizice a tranzistorului. Regimul se

obtine pentru (![]() si

si ![]() ).

).

zona rezistiva, in care tranzistorul se comporta ca o rezistenta

(rezistenta

dintre Drena si Sursa) a carei valoare este comandata

de valoarea tensiunii aplicata intre grila si sursa.

Regimul se obtine pentru tensiuni

mici de alimentare (![]() cu

cu ![]() ). Nu este folosit in cazul circuitelor logice, decat ca

zona de tranzitie.

). Nu este folosit in cazul circuitelor logice, decat ca

zona de tranzitie.

Din punctul de vedre al realizarii constructive ai tranzistorilor MOS ( cu canal p sau cu canal n) exista caracteristici comune si anume faptul ca :

zona drenei si zona sursei sunt realizate cu acelasi tip de

semiconductor (de tipul N la NMOS si P la PMOS), ceea ce face ca sa se inchida intre sursa si drena un curent de electroni in cazul NMOS si un curent de goluri in cazul PMOS;

zona drenei este separata de zona sursei prin substratul

realizat de alt tip decat cele doua zone (de tipul P la NMOS si N la PMOS);

grila este separata de substrat prin intermediul unei zone

izolatoare (un oxid);

Tehnologia de realizare a tranzistorilor MOS conduce la performante mai bune pentru NMOS, motiv pentru care PMOS se intalnesc numai la realizarea structurilor complementare de tipul CMOS.

De regula circuitul caracteristic al unei tehnologii este inversorul (circuitul care primind la intrare "0" logic forteaza iesirea in "1"logic si invers "1"logic la intrare determina "0" logic la iesire).

Inversorul in tehnologie NMOS

Cea mai simpla schema de inversor in tehnologie NMOS se obtine cu un tranzistor MOS cu canal indus in drena caruia se conecteaza un rezistor, ca in figura 4.17.

Fig. 4.17.

Modificand valoarea tensiunii de intrare Vise modifica tensiunea VGS = Vi iar curentul de drena creste conform caracteristicii statice de transfer din figura 4.15b.

Tensiunea de iesire calculata cu relatia

![]() ,

,

determina

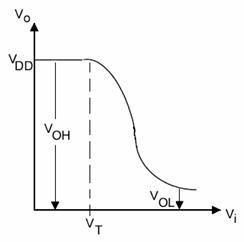

caracteristica de transfer a inversorului din figura 4.18.

Fig. 4.18.

Pentru tensiuni de intrare corespunzatoare valorii logice "0"![]() curentul iD prin tranzistor si prin RD este zero (vezi figura

4.15b, zona pentru

curentul iD prin tranzistor si prin RD este zero (vezi figura

4.15b, zona pentru ![]() ) ceea ce face ca

tranzistorul sa fie blocat si tensiunea la iesire sa

ramana la potentialul sursei de alimentare

) ceea ce face ca

tranzistorul sa fie blocat si tensiunea la iesire sa

ramana la potentialul sursei de alimentare ![]() , adica face ca iesirea sa fie "1"logic.

, adica face ca iesirea sa fie "1"logic.

Pentru tensiuni ![]() curentul iD creste dupa o

functie patratica cu tensiunea de intrare, motiv pentru care

tensiunea de iesire scade

curentul iD creste dupa o

functie patratica cu tensiunea de intrare, motiv pentru care

tensiunea de iesire scade ![]() , pana la V0L.

, pana la V0L.

La iesirea inversorului se va cupla intrarea unui alt circuit logic (de tipul MOS) care intrare reprezinta o sarcina capacitiva CS pentru inversor (de valoarea capacitatii de intrare a circuitului logic).

Comutarea intrarii inversorului din "0"in "1"logic (tranzistorul comuta din blocare in conductie ) determina descarcarea capacitatii CS prin tranzistor. Circuitul de descarcare este prezentat in figura 4.19a).

Iesirea inversorului comuta din "1"in "0"logic.

a)

b) Fig. 4.19.

Tensiunea de iesire se determina pe baza ecuatiilor circuitului (4.19a)

![]() ,

,

![]() ,

, ![]() ,

,![]() ,

,

adica a ecuatiei diferentiale a circuitului:

![]() .

.

Forma de unda la descarcarea condensatorului este prezentata in figura 4.20 pe intervalul (0,Tu ).

Circuitul de incarcare a capacitatii CS , prin RD de la sursa de alimentare catre VDD in intervalul in care tranzistorul este blocat, este prezentat in figura 4.19b). Variatia tensiunii de iesire a inversorului este conform variatiei tensiunii de pe condensator

![]() ,

,

cu forma de unda prezentata in figura 4.20 pe intervalul (Tu, T).

Viteza de

comutare depinde de constanta de timp de incarcare a condensatorului ![]() . Condensatorul ajunge repede la valoarea finala

daca rezistorul RD are

valori mici.

. Condensatorul ajunge repede la valoarea finala

daca rezistorul RD are

valori mici.

O rezistenta RD de valoare mica determina un potential ridicat al iesirii aflata in "0" logic (nerecomandat).

Pentru a realiza cele doua conditii contradictorii se inlocuieste RD cu o sarcina activa.(tranzistorul TS ) din figura 4.21.

Sarcina

activa este un tranzistor cu MOS cu canal initial cu saracire la

care grila este conectata la sursa. Se contata ca avem un

curent nenul prin tranzistor chiar la ![]() (vezi caracteristica statica din figura 4.15a).

(vezi caracteristica statica din figura 4.15a).

Fig. 4.21.

Tranzistorul TS se comporta ca o rezistenta avand doua valori distincte si anume o valoare mica atunci cand tranzistorul T este in conductie (tensiune de intrare Vi corespunzatoare valorii "1" logic) si o valoare foarte mare la blocarea tranzistorului T.

Sarcina activa va imbunatati fronturile impulsurilor de la iesirea inversorului.

La

comutarea iesirii din "0" in "1" logic tranzistorul T va comuta din zona activa in blocare. Tranzistorul TS fiind in conductie va

prezenta o rezistenta RS

de valoare mica, rezistenta prin care se va incarca

(rapid) capacitatea de intrare Cin a circuitului logic

cuplat la iesirea inversorului. Rezistenta fiind mica, contanta

de timp ![]() va fi mica

si viteza de crestere a tensiunii de iesire va fi mare (timpul

de stabilire a regimului permanent este

va fi mica

si viteza de crestere a tensiunii de iesire va fi mare (timpul

de stabilire a regimului permanent este ![]() ).

).

Inversorul in tehnologie CMOS

Inversorul CMOS are in componenta doi tranzistori complementari unul cu canal n (Tn ) si celalalt cu canal p (Tp ), conectati ca in figura 4.22. [29]

Caracteristicile statice de transfer pentru tranzistorii Tn si Tp sunt prezentate in figura 4.23.

Fig. 4.23.

Conform caracteristicilor

statice constatam ca in domeniul ![]() niciun tranzistor nu

este in conductie. Tehnologic cele doua tensiuni de prag sunt egale

(si de semn contrar)

niciun tranzistor nu

este in conductie. Tehnologic cele doua tensiuni de prag sunt egale

(si de semn contrar) ![]() .

.

In cazul seriei normale 4000 tensiunea de prag este VT = 1,5 V (in 1972 cand s-a lansat seria) apoi progresele tehnologice au scazut valoarea tensiunii de prag la VT = 1,0 V.

Nota: In cadrul figurii 4.23, pe langa caracteristicile statice ale tranzistorilor MOS, sunt prezente simbolurile tranzistorilor intr-o varianta simplificata (varianta similara tranzistorilor cu jonctiuni).

Schema inversorului din figura 4.22 este prezentata a) cu reprezentarea normala a tranzistorilor si b) cu reprezentarea simplificata a tranzistorilor MOS, reprezentare care va fi folosita in continuare.

Tensiunea VGSp este ceea ce ramane din tensiunea de alimentare dupa ce s-a scazut tensiunea Vi aplicata la intrarea inversorului, diferenta luata cu semnul minus.

Daca Vi = 0 tranzistorul Tn este blocat iar VGSp = - VDD iar tranzistorul Tp este in conductie. Iesirea este in "1"logic si Tp furnizeaza curent circuitului conectat la iesirea inversorului.

Daca Vi > VT tranzistorul Tn este in conductie iar VGSp are valori mai mici decat VT ceea ce face ca Tp sa se blocheze.

Se constata ca cei doi tranzistori conduc pe rand curentul electric de conductie.

De fapt caracteristica statica a inversorului, pe langa cele doua zone stabile a si b (prezentate mai sus) in care un tranzistor este blocat iar celalalt in conductie, are in compunere si zona de tranzitie c , ca in figura 4.24.

Vi Fig. 4.24.

Zona de tranzitie corespunde, la cresterea tensiunii de intrare, comutarii tranzistorului Tn din blocare in conductie si comutarii tranzistorului Tp din conductie in blocare.

Seria normala 4000 pentru circuite logice CMOS, la tensiuni de alimentare VDD = 3,,15 V (fara a depasi 18 V), are nivelele logice:

la iesire V0Hmin =VDD - 0,5 V, V0Lmax = 0,05 V,

la intrare VIHmin = 0,7 VDD , VILmax = 0,3 VDD,

Deoarece

tranzistorii au tensiuni de prag VT

= 1,5,.,1,0 V tensiunea

de alimentare nu poate fi scazuta sub 2 V (![]() ).

).

Marginea de zgomot este aceeasi :

ML =VILmax- V0Lmax = 0,3 VDD,

MH =V0Hmin - VIHmin = 0,3 VDD.

Timpul de propagare si puterea disipata in regim static depinde de materialul portii:

tp = 60 ns , ![]() , pentru poarta de Al,

, pentru poarta de Al,

tp = 40 ns, ![]() , pentru poarta de Si.

, pentru poarta de Si.

Timpul de propagare limiteaza frecventa de operare a circuitului la aproximativ 10 MHz (pentru tp = 100 ns).

Curentii de intrare au valori foarte mici si aume

![]() ,

,

iar valoarea maxima a curentului de iesire este

![]() .

.

Factorul de

bransament (n) reprezinta numarul maxim de porti care pot fi cuplate

la iesirea unei porti logice. Este limitat de regimul dinamic al

circuitului la n = 50 si nu de valoarea curentului absorbit de intrari (![]() ).

).

Seria rapida (High speed - CMOS) 74HC si 74HCT

Circuitele

din seria rapida asigura timpi de propagare de tp

= 9 ns la VDD

= 5 V (fata de seria

normala la care ![]() ) la o putere disipata de

) la o putere disipata de ![]() .

.

Cele doua marcaje (HC , HCT) din seria rapida CMOS difera prin valoarea tensiunii de alimentare. Pentru HC VDD =2,,6 V si pentru seria HCT VDD =4,5,,5,5 V. In plus seria HC nu poate fi comandata de circuite TTL (dar poate comanda sarcini TTL) pe cand seria HCT poate fi comandata de circuite TTL si poate comanda sarcini TTL (spunem ca este TTL compatibila).

Curentul de iesire maxim este:

I0 = 4 mA laHC,

I0 = 6 mA la HCT.

Exista serii realizate in tehnologie CMOS dar la care intrarea nu respecta standardul nivelelor logice de mai sus. Astfel exista serii CMOS cu intrari TTL numite 74FCT (Fast - CMOS), 74ACT 74AHCT (Advanced - High speed - CMOS) s.a.

Seria rapida (Advanced - CMOS) 74AHC, 74AHCT , 74ACT

Circuitele AHC folosesc o sursa de alimentare VDD= 2,0,,5,5 V.

Circuitele AHCT folosesc o sursa de alimentare VDD= 4,5,,5,5 V. Nivelele logice la VDD = 4,5 V sunt:

la iesire V0Hmin =VDD - 0,1 V, V0Lmax = 0,1 V,

la intrare VIHmin = 2,0 V , VILmax = 0,8 V,

marginea de zgomot MH = 2,4 V , ML = 0,7 V .

Iesirea in curent a circuitului este de I0max = 8 mA, putand comanda numai doua porti logice TTL (dar poate comanda foarte multe porti logice MOS, spre exemplu mai mult de 50 porti).

Timpul de propagare este tP = 3,7 ns, ceea ce permite circuitului sa functioneze pana la frecvente de 170 MHz.

De fapt seria rapida (Advanced) a fost gandita in scopul inlocuirii seriei rapide in conditiile utilizarii unor surse de alimentare de tensiune continua redusa (VDD= 3,3 V) pentru cresterea performantelor in regim dinamic si in regim static.[15]

Pentru VDD= 3,3 V iesirea in curent a circuitului este de I0max = 4 mA.

Tensiunile

de prag ale tranzistorilor au fost scazute la ![]() pentru seria AHC

si la

pentru seria AHC

si la ![]() pentru seria AHCT.

pentru seria AHCT.

Circuitele

ACT sunt caracterizate printP = 5 ns, la ![]() , ceea ce permite circuitului sa functioneze

pana la frecvente de 160 MHz.

Iesirea in curent a circuitului are valori mari, de pana la I0max = 24 mA.

, ceea ce permite circuitului sa functioneze

pana la frecvente de 160 MHz.

Iesirea in curent a circuitului are valori mari, de pana la I0max = 24 mA.

S-au realizat serii cu tensiune de

alimentare redusa" LV (Low

Voltage) in scopul utilizarii in scheme electronice de comanda

alimentate la tensiuni mai joase de 5 V (tensiuni

de alimentare standardizate ![]() ,

, ![]() ,

, ![]() ), de regula

pentru aparate portabile a caror sursa de energie este un acumulator.

), de regula

pentru aparate portabile a caror sursa de energie este un acumulator.

Aparitia

seriilor cu tensiuni de alimentare reduse are o justificare tehnologica in

sensul ca scaderea ariei pe care sunt implementati tranzistorii

conduce la scaderea fiabilitatii circuitului logic alimentat la

tensiuni mari. Astfel un CI realizat in tehnologia ![]() nu va mai

functiona stabil la 5 V ci numai

la o tensiune de alimentare de 3,3 V,

iar unul realizat in tehnologia

nu va mai

functiona stabil la 5 V ci numai

la o tensiune de alimentare de 3,3 V,

iar unul realizat in tehnologia ![]() va trebui alimentat la

2,5 V.

va trebui alimentat la

2,5 V.

In aceasta categorie se incadreaza circuitele 74LV (Low Voltage), 74LVC, 74ALVC (Advanced Low-Voltage CMOS), 74AVC (Advanced Very-low-voltage CMOS), 74AUC (Advanced Ultra low voltage CMOS).

In tabelul 3 sunt prezentate principalele caracteristici ale circuitelor din seria cu tensiune de alimentare redusa.

Tabelul 3.

|

Circuitul |

74LV |

74LVC |

74ALVC |

74AVC |

74AUC |

|

Domeniul VDD [V] |

|

|

|

|

0,8,.,2,7 |

|

tP[ns] |

9,.,14 9 |

4,.6.5 5 |

2.2,.,4 3 |

3.2 / 1.9 |

1.5 |

|

I0max[mA] |

8 |

24 |

24 |

8 |

8 |

|

tP si I0max pentru VDD |

3.3 V |

3.3 V |

3.3 V |

1.8 V/ 2.5 V |

1.8 V |

Scaderea tensiunii de alimentare modifica valorile tensiunilor asociate nivelelor logice.

Spre

exemplu in cazul circuitelor din seria 74ALVC, pentru o tensiune de alimentare

de VDD = 3,3 V , valoarea

maxima de "0" logic este ![]() iar valoarea

minima asociata starii "1" logic este

iar valoarea

minima asociata starii "1" logic este ![]() . Timpul de propagare a semnalului de la intrare la

iesire este de

. Timpul de propagare a semnalului de la intrare la

iesire este de ![]() .

.

Seriile 74LCX si 74VCX difera prin valorile permise ale tensiunilor de

alimentare, prima are ![]() iar a doua

iar a doua ![]() .

.