|

|

|

Proiectare Entities

Scop: capitolul introduce proiectarea entitatilorca o componenta principala a VHDL in vederea descrierii hard pentru proiectare ierarhizata.

1 Entity(utilizata pentru a descrie complet un bloc hardwardware)

In proiectarea entitatilor exista 3 sectiuni :

Entity: cuprinde pinii functiunii.Cuvantul cheie este port cu in/out.

Std_logic :standard logic(tipul portului i/o) ;se gaseste in library IEEE.STD_LOGIC_1164.all.

Pentru ex.1:entitatea are structura tipica prezentata in ex.1.

Architecture : implementeaza functiunea.

Architecture nume_architecture of nume_entity is

Begin

Corp_entitate;

End nume_architecture;

<=:operator de asignare:valoarea calculate in dreapta trece in variabila din stanga.Expresie ce utilizeaza intrari.

Data type:STD_LOGIC : reprezinta valori binare ce apartin-ca valori binare

Incluse in library STD_LOGIC_1164.all;

!!!VHDL NU ESTE CHASE SENSITIVE !!!

2.2 Semnale : componente ce sunt inauntrul Black Box,nu ce apar la pini !

Caracterizeaza conexiunile interne in descrierea entity.

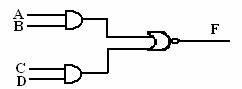

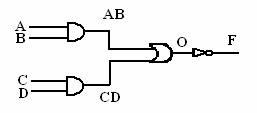

Pentru exemplul 2 :

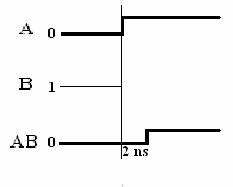

after 2 ns ;:intarzieri introduse de programator.var<=(functie) after n ns ;forteaza o intarziere~cu timpul de propagare a portilor.Sintetizatorul nu ia la compilare intarzierea.

O entitate poate avea mai multe arhitecturi ce caracterizeaza diferit functiunea inclusa.

Signal apare in arhitectura inainte de begin.Signal nume_semnal: tip;

Semnalele nu sunt considerate in/out!

Fiecare functie descrisa in corpul arhitecturii este asignata concurent !(ordinea asignarii nu are importanta asupra functionarii).Aceasta se intampla pentru ca mai multe circuite pot functiona simultan!

3 ASIGNARE CONCURENTA

Un semnal concurent este conditionat de eveniment(evenimente).In exemplul urmator,are loc schimbarea de stare logica la intrarile retelei de asignare.

delay total in out=5ns pentru ca AB si CD:paralele=>numai 2 ns sin u 4 ns.

Delay este important pentru simulare pentru ca la acest nivel pot introduce intarzieri echivalente cu cele fizice(timp de propagare).La sinteza automata,compilatorul ignora aceste delay-uri prezente in alocarea semnalelor.

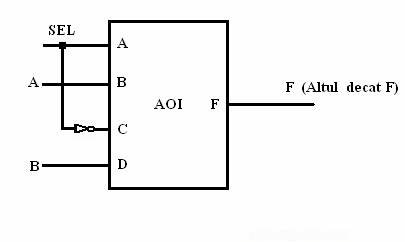

4 COMPONENT

Scopul introducerii componentelor este :permite construirea de ierarhii in proiectare.Cum e declaratia la entity,la fel trebiue sa apara declaratia si la component.

Port map :leaga componentele,indica legatura dintre i/o declarate in cadrul componentei respective si i/o declarate in arhitectura.

Pentru exemplul 3:

Fiecare nivel inferior al entitatii din exemplul 3 trebuie declarat ca si component in cadrul arhitecturii functiunii noi.

Declaratia este de forma:

Component nume_componenta

port (nume_in:in_tip ;

nume_out :out_tip) ;

End_component

Component este similara cu n cipuri conectate pe o placa.Orice componenta trebuie sa fie legata in cadrul arhitecturii functiunii noi:apare un label:G1:INV port map(SEL,SELB) ;

G2 :AOI port map (SEL,A,SELB,B,F) ;

Port map pentru o componenta are un numar de variabile egal cu suma in+out,declarate in port la nivelul component sau entity.

Variabilele ce apar in port map sunt numai in sau out ale noii functiuni mux2 si signal declarate in corpul arhitecturii lui mux

La firul care nu are label, il vom declara ca signal.

Utilizarea component este foarte importanta in sinteza :permite ca ierarhia unei proiectari sa fie controlata prin scrierea de cod VHDL.

5 STANDARD LOGIC VECTOR

STD_LOGIC :descrie bitul ce apartine.

B<='0' ;lui B i se atribuie valoarea bit '0' logic.

STD_LOGIC cuprinde :'0','1','u','z','x' ;

u :neidentificat ;

z :starea de inalta impedanta;

x:necunoscut;

STD_LOGIC_VECTOR:descrie un cuvant,mai multi biti ,o magistrala.Se utilizeaza pentru a

descrie BUS-uri,vectori.Este de tip array.

Exemplu :

SIGNAL V :STD_LOGIC_VECTOR(7 downto 0);

V<="8";(in hexazecimal)

V<="0101xxxx";

V(7)<=V(6);(deplasare stanga la nivel de biti)=>V(7)='1'.

signal V :STD_LOGIC_VECTOR (7 downto 0);

W :STD_LOGIC_VECTOR(0 to 3);

W<=V(7 downto 4);=>W(0)=V(7);W(1)=V(6);W(2)=V(5);W(3)=V(4);

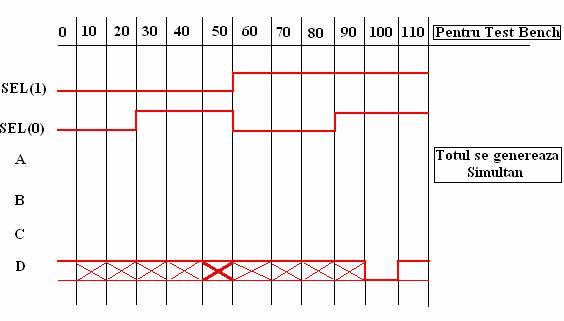

6 TEST BENCHES (secventa de test)

La sinteza nu este luata in considerare,face doar o simulare.

Test bench creeaza stimulii de test care se aplica functiunii ,leaga stimulii.

Caracteristici test bench:

Pentru o simulare VHDL este necesara:

Cea de-a doua descriere reprezinta test bench-ul.

Functiunea principala a test bench-ului este de a genera o secventa de stimuli cu verificare controlata in timp .Aceste semnale se leaga la intrarea functiunii de testat .Prin simulare,designer-

ul urmareste si depaneaza functiunea testate.

Sintaxa unui test bench cu referire la exemplul 5 :

library ...

entity test_mux4 is

empty(gol)

end;

architecture test_bench of test_mux4 is

component mux4

end_component

signal declarations:toate in/out functiunii testate.

Begin

sel<="00","01" after.,"10"after.,.;

Delay-urile au originea timpului egale cu inceputul simularii.Componenta din exemplul 5 este

legata de stimuli cu port map vezi exemplul 3.

7 CONFIGURATII

Asa cum s-a precizat, o proiectare in VHDL consta in:

cod pentru mai multe entitati reprezentand corpuri ierarhice ;

cateva pachete ce contin definitii comune. ;

In scopul simularii si sintezei unei ierarhii,trebuie sa selectam entitatea si

arhitectura,care sa fie utilizate pentru fiecare componenta alocata in cadrul

ierarhiei.Pentru a selecta arhitectura unei componente din mai multe posibile,

VHDL dispune de CONFIGURATION.

Configuration reprezinta o parte separata de cod VHDL.Trebuie sa aiba un nume si selecteaza arhitectura dorita pentru functiunea de implementat.

Sintaxa :

configuration nume_config of nume_entity is

for nume_architecture

end for;

end [nume_config];

Nota:configuration se refera la test bench.O configuratie se refera tot la o entity plasata la nivel mai ridicat si configureaza o arhitectura.