|

|

|

Electrotehnica si Informatica

Calculatoare

ISTEME MULTIMICROPROCESOR

1.Definirea temei si cerintele

memorie SRAM de 6K cu circuite 2142;

memorie DRAM de 32K cu circuite 2118;

Interfata I/O cu 2 circuite 8282 ;

Pentru tratarea intreruperilor se va folosi circuitul 8259A. In cazul circuitelor programabile se vor prezenta secvente de program pentru aducerea acestora in stare operationala. Se cere schema electrica a modulului, realizata cu un program de proiectare asistata pe calculator.

2.Schema bloc a sistemului.

In figura 1 se prezinta schema bloc a modulului proiectat. In aceasta schema se prezinta atat circuitele utilizate cat si interconexiunile dintre ele, la nivel de principiu.

Accesarea resurselor locale sau a celor din

sistem e comandata de semnalul SYSB/ ![]() . Pentru situatia in care acest semnal devine "0" se face acces la

resursele locale, in caz contrar accesul se face la resursele externe. Schema

bloc a modulului contine urmatoarele elemente:

. Pentru situatia in care acest semnal devine "0" se face acces la

resursele locale, in caz contrar accesul se face la resursele externe. Schema

bloc a modulului contine urmatoarele elemente:

Microprocesorul (8086) care lucreaza la modul maximal.

Generatorul de tact (8284) folosit pentru generarea tactului necesar microprocesorului pentru a asigura functionarea circuitelor interne ale acestuia. Circuitul (8284) face divizarea cu trei a frecventei determinate de cuartul ce se conecteaza la el.

Controler de magistrala (8288) care, prin decodificarea semnalelor de stare (S0,S1,S2) furnizeaza semnalele de comanda corespunzatoare.

Latch de adrese (8282), pentru generarea magistralei interne de adrese, realizata prin demultiplexarea semnalelor AD0-AD15 si A16-19.

Buffer de date (8286), pentru generarea magistralei interne de date , realizata prin demultiplexarea semnalelor AD0-AD15.

Un bloc de memorie EPROM (2732).

Un bloc de memorie SRAM (2142).

Un bloc de memorie DRAM (2118).

Decodificator de adresa (8205) pentru selectarea blocurilor de memorie.

Controler de reimprospatare (8202) pentru reimprospatarea blocului de memorie DRAM.

Circuit de interfata I/O (8282) si Conectorul de interfete pentru conectarea sistemului cu exteriorul.

Bloc de interfata cu Magistrala Sistem care face legatura dintre modul si sistemul multimicroprocesor. Blocul este format din

a). Arbitru de magistrala (8289).

b). Controler de magistrala (8288).

c). Buffer de date (8287).

d). Latch adrese (8283).

Controler de intreruperi (8259).

Conector de magistrala multibus.

3.Intocmirea repartizarii spatiului de adrese.

A19A18A17A16

A15A14A13A12A11A10A9A8A7A6A5A4A3A2A1

A0

Adr.

in

HEX

0 1 11

01 11

00 0 0 0 0 0 0 0 0 0 0 0 0 0

. . .. . . . . . .. .

1111 1 1 1 1 1 1 1 1 1 1 1

0

.

1

70000

BFFFF

Pentru circuitul 8259A avem nevoie de doua locatii de memorie corespunzatoare celor doua porturi. Deci pentru A0=0 si A0=1 se aloca primele doua adrese pare din spatiul de memorie alocat pentru intreruperi (00 si 02

In ceea ce priveste circuitele de interfata I/O - circuitul 8255 este "vazut" de microprocesor ca un ansamblu de 4 adrese, deci i s-au repartizat urmatoarele 4 adrese pare (deoarece transferul cu microprocesorul se face pe 8 biti, in acest caz pe liniile inferioare ale magistralei de date, D0-D7) din spatiul de 64K, destinat operatiilor de intrare-iesire.

FFFFF

FC000

EPROM 16K

LIBER

BFFFF

70000

MEMORIE EXTERNA

512k

LIBER

0BFFF

08000

SDRAM 6K

07FFF

00000

DRAM 32K

8282

08

07

8282

06

05

8282

04

8259A pt. A0=1

03

02

8259A pt. A0=0

01

4. Proiectarea unitatii centrale.

Realizarea acestei etape presupune detalierea schemei bloc a unitati centrale, punandu-se in evidenta numarul de circuite utilizate si modul lor de conectare.

In configuratia multimicroprocesor cum este sistemul MULTIBUS,

microprocesorul 8086 lucreaza in mod maxim, fapt evidentiat prin

legarea la masa a intrarii MN/![]() . In aceasta situatie o parte din pini isi

schimba semnificatia, iar microprocesorul nu genereaza direct

semnalele de comanda, ci livreaza in fiecare ciclu de magistrala

un cuvant de stare controlerului de magistrala, care este

raspunzator de decodificarea cuvantului de stare si generarea

semnalelor de comanda corespunzatoare. Validarea acestui circuit se

face numai cand microprocesorul cere un acces la resursele locale (SYSB/

. In aceasta situatie o parte din pini isi

schimba semnificatia, iar microprocesorul nu genereaza direct

semnalele de comanda, ci livreaza in fiecare ciclu de magistrala

un cuvant de stare controlerului de magistrala, care este

raspunzator de decodificarea cuvantului de stare si generarea

semnalelor de comanda corespunzatoare. Validarea acestui circuit se

face numai cand microprocesorul cere un acces la resursele locale (SYSB/ ![]() =0).

=0).

Demultiplexarea magistralei comune in cea de date si cea de adrese este realizata cu ajutorul latch-urilor de adrese - 8282 (3 la numar), respectiv de buffer-ele de date - 8286 , circuitele fiind selectate prin semnalele corespunzatoare.

Circuitul 8284 furnizeaza microprocesorului semnalul de tact (CLK) avand frecventa de 5Mhz, prin divizarea cu 3 a frecventei oscilatorului sau intern. De aceea intre pinii x1 si x2 s-a conectat un cristal de cuart, avand frecventa de 15 Mhz. 8284 ofera, de asemenea, microprocesorului si semnalele: READY (caz in care trebuie prevazuta introducerea de stari de asteptare, daca este cazul, cat si sincronizarea, obligatorie, cu operatiile de pe magistrala MULTIBUS, cu ajutorul semnalului XACK), RESET (caz in care se necesita conectarea unor componente suplimentare astfel incat initializarea sa se produca la conectarea tensiunii de alimentare sau la apasarea unui buton de initializare, notat in schema cu Reset).

Schema detaliata se poate analiza in figura 2.

5. Proiectarea memoriei.

In cadrul acestui capitol se va expune fiecare bloc de memorie (EPROM, SRAM, DRAM), aratandu-se modul de obtinere si de conexiune a semnalelor de selectie si a celor de comanda.

Inaintea proiectarii se impun cateva observatii comune celor trei tipuri de memorii. Data fiind organizarea pe bancuri a blocurilor de memorie (magistrala de date de 16 biti fiind impartita in magistrala: inferioara, D0-D7, si cea superioara, D8-D15) memoria va fi distribuita in mod egal in cele doua blocuri, astfel incat locatiile de adresa succesiva vor fi regasite in bancuri diferite (cele cu adrese pare in bancul inferior, iar cele cu adrese impare in bancul superior). Acest mod de organizare a memoriei permite transferul de date pe octet pe una din cele doua bancuri in functie de semnalele A0 si nBHE, sau pe cuvant.

O alta observatie se poate face cu privire la timpul de acces al memoriei: 2T>tacces. Daca timpul de acces este mai mare decat doua perioade de tact atunci este nevoie adaugarea unei logici de inserare a unor stari de asteptare in activitatea microprocesorului, pentru ca transferul datelor sa se realizeze corect. Circuitele utilizate in proiectare sunt:

EPROM 2716 avand tacces=350 ns

SRAM2142 avand tacces=150 ns

DRAM 2118 avand tacces=100 ns

2T = 400 ns

Se observa ca nici un tip de memorie din cele trei nu necesita o astfel de logica pentru inserarea de stari WAIT.

5.1. Circuitul de memorie EPROM (2732)

Circuitul de memorie 2732 are capacitatea de 4Kx8. Asadar, pentru obtinerea celor 16K de care avem nevoie vom utiliza 8 circuite (4 in bancul inferior si 4 in cel superior).

Pentru obtinerea semnalelor de selectie vom intocmi tabelul adreselor limita pe baza hartii realizate in capitolul 3. Acest tabel arata astfel:

A19A18A17A16A15A14A13

A12A11A10A9A8A7A6A5A4A3A2A1

A0

Adresa

in

HEXA

Semnal

De

selectie

111111 0

.. . . . ..

111111 0

000 0 0 0 0 0 0 0 0 0

. . . . .. . . . . . .

111 1 1 1 1 1 1 1 1 1

0

.

1

FC000

FDFFF

EPROM1

111111 1

.. . . . ..

111111 1

000 0 0 0 0 0 0 0 0 0

. . . . .. . . . . . .

111 1 1 1 1 1 1 1 1 1

0

.

1

FE000

FFFFF

EPROM2

Liniile de adrese: A0 - selectie banc

A1 - A12 - selectie in interiorul circuitului de memorie

A13 - A19 - selectie circuit

Sensul transferului este, in cazul acestui tip de

memorie, unidirectional, accesul fiind numai pentru citire, deci se poate

renunta la semnalele pentru validarea bancurilor: A0 si ![]() .

.

Schema de conectare si comanda a memoriei EPROM este data in figura 3.

5.2. Circuitul de memorie SRAM (2142)

Circuitul de memorie 2142 are capacitatea de 1Kx4. Pentru a forma 1Kx8 avem nevoie de 2 circuite ce lucreaza in paralel, conform acestui rationament pentru a forma 8K de care avem nevoie vom utiliza 12 de circuite (6 in bancul superior si 6 in cel inferior).

Conform hartii de memorie realizate in capitolul 3 putem intocmi urmatorul tabel al adreselor limita. Acest tabel arata astfel:

A19A18A17A16A15A14A13A12A11

A10A9A8A7A6A5A4A3A2A1

A0

Adresa

in

HEXA

Semnal

De

selectie

0000 1 0 000

000010 00 0

0 0 0 0 0 0 0 0 0 0

. . .. . . . . . .

1 1 1 1 1 1 1 1 1 1

0

.

1

08000

087FF

SRAM1

000010 001

000010 00 1

0 0 0 0 0 0 0 0 0 0

. . .. . . . . . .

1 1 1 1 1 1 1 1 1 1

0

.

1

08800

08FFF

SRAM2

00001 0 010

00001 0 01 0

0 0 0 0 0 0 0 0 0 0

. . .. . . . . . .

1 1 1 1 1 1 1 1 1 1

0

.

1

09000

097FF

SRAM3

Semnificatia liniilor de adrese este urmatoarea:

A0 - selectie banc

A1 - A10 - selectie in interiorul circuitului de memorie

A11 - A19 - selectie circuit

Sensul transferului este, in cazul acestui tip de memorie, bidirectional, accesul fiind atat pentru citire cat si pentru scriere.

![]() Pentru sinteza semnalului

de selectie s-a folosit decodificatorul 8205, iar pentru selectia

bancului s-a folosit linia A0 - pentru bancul inferior, respectivBHE - pentru

bancul superior.

Pentru sinteza semnalului

de selectie s-a folosit decodificatorul 8205, iar pentru selectia

bancului s-a folosit linia A0 - pentru bancul inferior, respectivBHE - pentru

bancul superior.

Pentru sinteza semnalelor de selectie: SRAM1,SRAM2 s-a observat ca putem utiliza acelasi decodificator folosit pentru selectia circuitului EPROM. Deci ecuatia intrarii E3 a decodificatorului 8205 este:

![]()

Schema de conectare si de comanda a memoriei SRAM este data in figura 4.

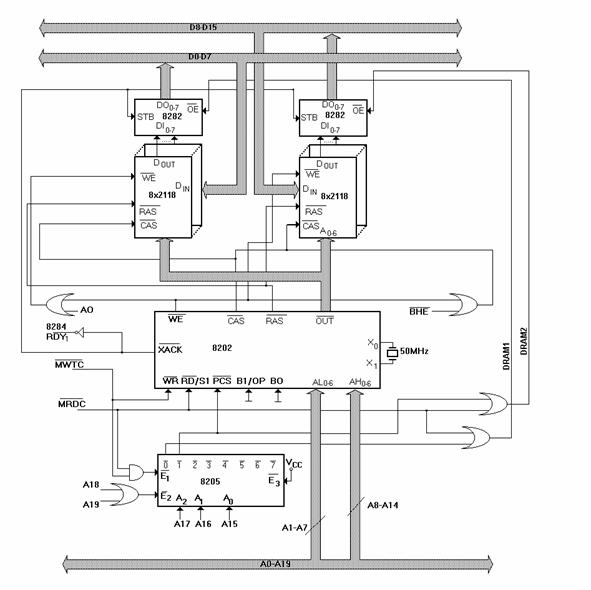

5.3. Circuitul de memorie DRAM (2118)

Circuitul de memorie 2118 are capacitatea de 16Kx1. Pentru a forma 16Kx8 avem nevoie de opt circuite ce lucreaza in paralel, conform acestui rationament pentru a forma 32K de care avem nevoie vom utiliza 16 de circuite (8 in bancul superior si 8 in cel inferior).

Acest tip de memorie necesita

reimprospatarea periodica a informatiei, astfel incat in

schema trebuie adaugat un controler de reimprospatare (8202).

Acesta, pe langa reimprospatarea periodica a celulelor de

memorie, realizeaza si multiplexarea liniilor de adrese, furnizand

circuitelor adresa de rand insotita de semnalul ![]() si cea de

coloana insotita de semnalul

si cea de

coloana insotita de semnalul ![]() , deoarece circuitul prezinta o structura

interioara de tip matriciala. Pentru a determina valoarea

numerica a frecventei cristalului ce trebuie conectat la controler

s-au comparat datele de catalog pentru memoria DRAM (2118), pentru care timpii

de acces este tacc= 100ns, si diagramele de timp ale

circuitului 8202. Urmarea acestei comparatii a dus la concluzia

satisfacerii urmatoarelor relatii:

, deoarece circuitul prezinta o structura

interioara de tip matriciala. Pentru a determina valoarea

numerica a frecventei cristalului ce trebuie conectat la controler

s-au comparat datele de catalog pentru memoria DRAM (2118), pentru care timpii

de acces este tacc= 100ns, si diagramele de timp ale

circuitului 8202. Urmarea acestei comparatii a dus la concluzia

satisfacerii urmatoarelor relatii:

7.TCTR=100ns

conform careia frecventa de lucru a circuitului 8202 trebuie sa fie:

![]()

De aceea, intre intrarile: X0 /OP2 , X1 /CLK s-a conectat un cristal de cuart cu aceasta frecventa.

Conform hartii de memorie prezentate in capitolul 3 putem intocmi urmatorul tabel al adreselor limita pentru blocurile de memoria DRAM:

A19A18A17A16A15

A14A13A12A11A10A9A8A7A6A5A4A3A2A1

A0

Adresa

in

HEXA

Semnal

De

selectie

00000

.. . . .

00000

0 0 000 0 0 0 0 0 0 0 0 0

. .. . . . . . . . .

1 1 111 1 1 1 1 1 1 1 1 1

0

.

1

00000

07FFF

DRAM

Semnificatia liniilor de adrese este urmatoarea:

A0 - selectie banc

A1 - A12 - selectie in interiorul circuitului de memorie

A13 - A19 - selectie circuit

Semnalul de selectie a blocului DRAM

provenit de la decodificatorul 8205 se va aplica intrarii ![]() a controlerului 8202

si va fi folosit pentru deschiderea buffer-elor 8282 in cazul unei comenzi

de citire. Circuitul furnizeaza si un semnal de confirmare a

transferului

a controlerului 8202

si va fi folosit pentru deschiderea buffer-elor 8282 in cazul unei comenzi

de citire. Circuitul furnizeaza si un semnal de confirmare a

transferului ![]() care este conectat

prin intermediul unui inversor la intrarea RDY1 a

generatorului de tact 8284. Lucrand cu blocuri de 16K, B0 s-a

legat la masa, in acest caz folosindu-se doar semnalul

care este conectat

prin intermediul unui inversor la intrarea RDY1 a

generatorului de tact 8284. Lucrand cu blocuri de 16K, B0 s-a

legat la masa, in acest caz folosindu-se doar semnalul ![]() pentru

esantionarea adresei de rand.

pentru

esantionarea adresei de rand.

Pentru a mentine datele citite din memorie

pe magistrala un timp suficient pentru a fi preluate corect de

microprocesor, am intercalat intre iesirile circuitelor de memorie si

magistrala doua latch-uri pentru date (8282). Inscrierea datelor in

latch-uri se face cu ajutorul semnalului ![]() , iar validarea iesirii cu

, iar validarea iesirii cu ![]() si semnalul de

selectie a blocului de circuite.

si semnalul de

selectie a blocului de circuite.

Schema blocului de memorie DRAM este data in figura 5.

6. PROIECTAREA INTERFETELOR DE INTRARE IESIRE

Pentru implementarea operatiilor de intrare/iesire paralele am folosit doua circuite 8282

Poturile acestor circuite pot lucra atat pentru intrarea cat si pentru iesire.Pentru tratarea intreruperilor am folosit un circuit 8259A.

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3

A2 A1 A0

Adresa

Obs

000 0 0 0 0 0 0 000

000 0 0 0 0 0 0 000

000 0 0 0 0 0 0 000

000 0 0 0 0 0 0 000

000

010

100

110

0000h

0002h

0004h

0006h

Date A

Comenzi A

Date B

Comenzi B

000 0 0 0 0 0 0 001

000 0 0 0 0 0 0 001

000 0 0 0 0 0 0 001

000 0 0 0 0 0 0 001

000

010

100

110

0008h

000Ah

000Ch

000Eh

Date A

Comenzi A

Date B

Comenzi B

000 0 0 0 0 0 0 000

000 0 0 0 0 0 0 000

001

011

0001h

0003h

8259A

Pentru circuitele 8282 am alocat adresele pare iar pentru circuitul 8259A adresele impare.

Circuitul 8259A este controler de intreruperi. Modul in care se conecteaza nivelele de intrerupere ale lui 8259A la liniile de intrerupere ale magistralei MULTIBUS si la sursele locale de intrerupere este lasat la latitudinea utilizatorului; in acest scop au fost prevazute conexiuni prin strapuri. Conectarea circuitului se face ca in figura 6.1.

|

|

Fig.6.1

7. SCRIEREA PROGRAMELOR PENTRU CIRCUITELE DE

INTERFATA

Programele de intrare a acestor circuite vor fi plasate in memoria EPROM la fiecare pornire sau RESET vor fi executate .Tot aici vor introduce programele de comunicatie paralela.

Circuitul 8259 se programeaza inmod singular, intrari active pe nivel, intreruperi vectorizate, achitare automata a intreruperii, prioritati rotitoare.

Secventa de program este urmatoarea:

MOV AL, 1Bh ;programare 8259A

OUT 12h,AL ; mod singular, intreruperi active pe nivel

MOV AL, 38h ;inscrierea vectorului

OUT 12h,AL ;de intrerupere

MOV AL, 0Fh ;achitare automata

OUT 12h,AL ;

MOV AL, 80h ;prioritati rotitoare

OUT 12h,AL ;

MOV AL, 3Ch ;programare 8282A

OUT 0Eh,AL ;canal 0, numsrare in binar

MOV AL, 41h ;incarcare constanta de numarare

OUT 0Eh,AL ;

MOV AL, 52h ;programare 8282A

OUT 06h,AL ;mod asincron, 1 bi de STOP, paritate impara, caractere ;de 5 biti, divizare cu 16 a tactului

MOV AL, 0Fh ;validare receptie si transmisie

OUT 06h,AL ;

Programul pentru circuitul 8282:

MOV A,0000h

OUT (0002),A

MOV A,0004,A

OUT (0006),A

MOV A,VECT

RETN

8. PROIECTAREA BLOCULUI DE INTERFATA CU MAGISTRALA SISTEM

Circuitele utilizate pentru realizarea BIM-ului sunt urmatoare:

1x8289 -Arbitru magistrala

1x8289 -controler magistrala

2x8287 -buffer pentru magistrala externe de date

3x8283 - latch pentru magistrala externa de adrese

Circuitul 8259A de pe placa accepta o intrare ADR0/ADR13/

Schema bloc a blocului de interfata cu magistrala sistem este prezentata in figura 8.1.

9. ELABORAREA SCHEMEI ELECTRICE DE ANSAMBLU

Elaborarea schemei electrice de ansamblu al calculatorului monoplaca SBC se prezinta in ANEXA .